Trigger delay advanced register – ALLIED Vision Technologies Pike F-1600 User Manual

Page 212

Controlling image capture

PIKE Technical Manual V5.1.2

212

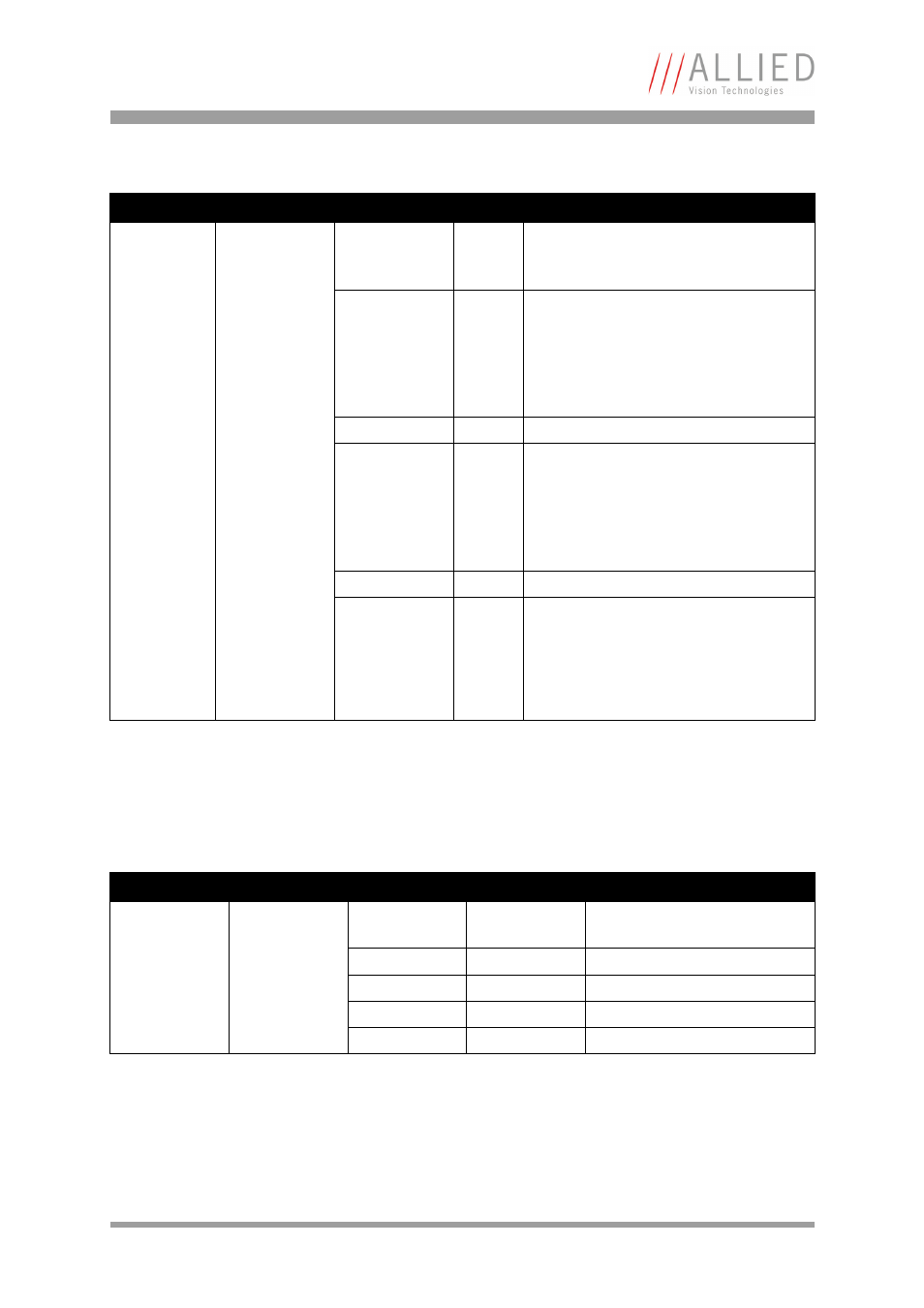

Trigger delay advanced register

In addition, the cameras have an advanced register which allows even more pre-

cise image capture delay after receiving a hardware trigger.

The advanced register allows start of the integration to be delayed by max.

2

21

μs, which is max. 2.1 s after a trigger edge was detected.

Register

Name

Field

Bit

Description

0xF0F00834

TRIGGER_DELAY Presence_Inq

[0]

Presence of this feature:

0: N/A

1: Available

Abs_Control

[1]

Absolute value control

O: Control with value in the Value field

1: Control with value in the Absolute

value CSR

If this bit = 1, the value in the Value field

has to be ignored

-

[2..5]

Reserved

ON_OFF

[6]

Write: ON or OFF this feature

Read: read a status

0: OFF

1: ON

In this bit = 0, other fields will be read

only.

-

[7..19]

Reserved

Value

[20..31] Value

If you write the value in OFF mode, this

field will be ignored.

If ReadOut capability is not available,

then the read value will have no meaning.

Table 69: CSR: Trigger delay

Register

Name

Field

Bit

Description

0xF1000400

TRIGGER_DELAY Presence_Inq

[0]

Indicates presence of this fea-

ture (read only)

---

[1..5]

-

ON_OFF

[6]

Trigger delay on/off

---

[7..10]

-

DelayTime

[11..31]

Delay time in μs

Table 70: Advanced CSR: Trigger delay