2 instructions – Omron SYSMAC CP CP1E-N@@D@-@ User Manual

Page 99

2-63

2 Instructions

CP1E CPU Unit Instructions Reference Manual(W483)

Tim

er and

Cou

nter

I

n

stru

ctio

ns

2

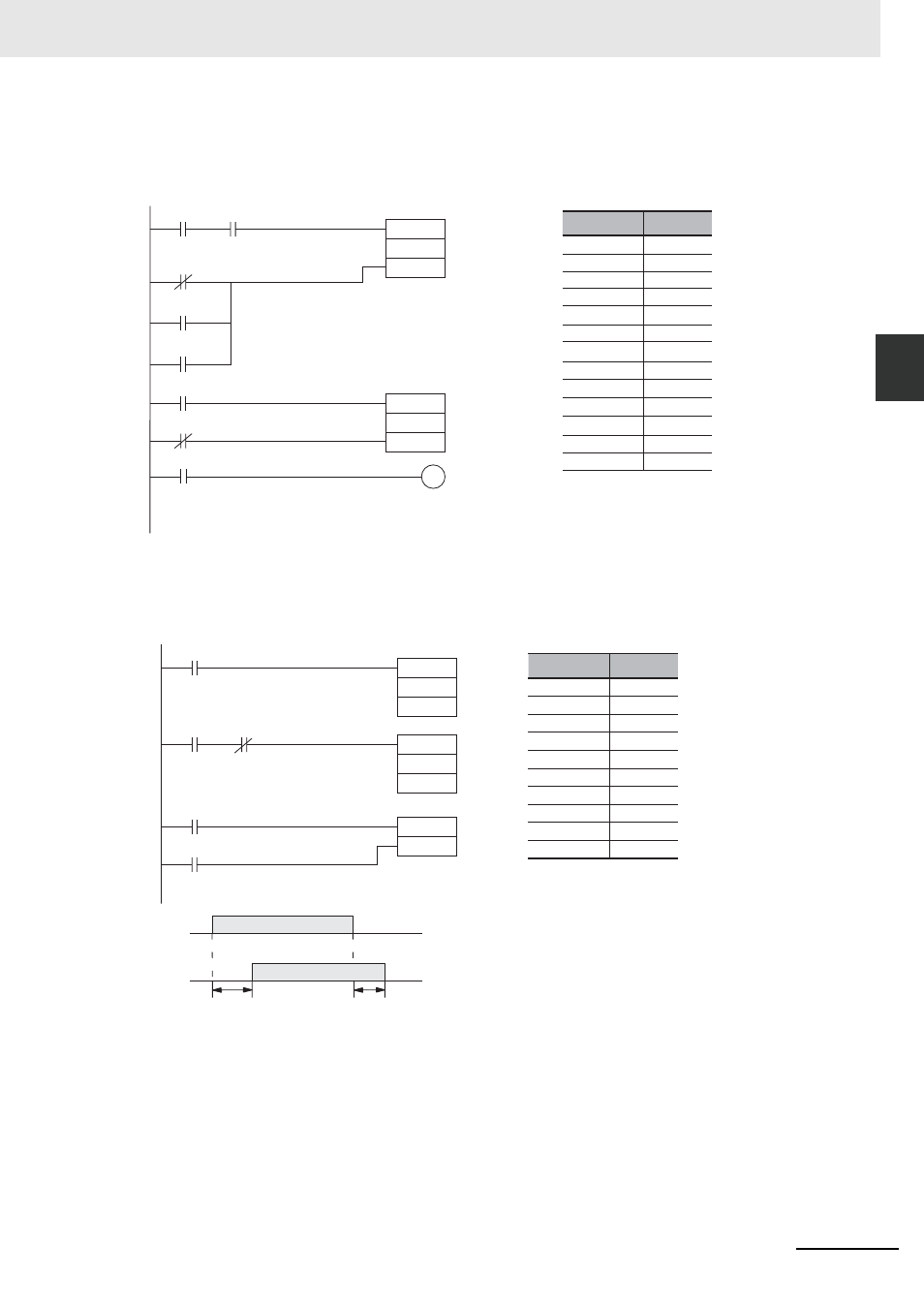

Example 2: Two-stage Counter

When an SV higher than 9999 is required, two counters can be combined as shown in the following

example. In this case, two CNT instructions are combined to make a BCD counter with an SV of

20,000.

Example 3: ON/OFF Delay

In this example two TIM timers are combined with KEEP(011) to make an ON delay and an OFF delay.

CIO 5.00 will be turned ON 5.0 seconds after CIO 0.00 goes ON and it will be turned OFF 3.0 seconds

after CIO 0.00 goes OFF.

CNT

0001

#0100

0.00

0.01

0.02

C0001

C0002

C0002

100.03

CNT

0002

#0200

C0001

0.02

(100 times)

(200 times)

Operands

0.00

#0100

#0200

Instruction

LD

C0001

LD

C0002

LD

0.01

AND

C0001

OR

C0002

OR

1

CNT

100.03

OUT

2

CNT

0.02

LD NOT

0.02

LD NOT

TIM

0001

#0050

0.00

TIM

0002

#0030

5.00

0.00

KEEP

100.05

T0001

T0002

0.00

100.05

5.0 s

3.0 s

Instruction

TIM

2

TIM

1

#0050

LD

5.00

LD NOT

0.00

#0030

LD

T0001

LD

T0002

KEEP(011)

100.05

LD

0.00

Operands