Precautions, Sample program, 2 instructions – Omron SYSMAC CP CP1E-N@@D@-@ User Manual

Page 164: Shift register exceeding 16 bits

2 Instructions

2-128

CP1E CPU Unit Instructions Reference Manual(W483)

Precautions

• Do not use more than one SFT(010) instructions with overlapping shift words. The results will not be

dependable.

• St and E must be in the same data area.

• The bit data shifted out of the shift register is discarded.

• When the reset input turns ON, all bits in the shift register from the rightmost designated word (St) to

the leftmost designated word (E) will be reset (i.e., set to 0). The reset input takes priority over other

inputs.

• St must be less than or equal to E, but even when St is set to greater than E an error will not occur

and one word of data in St will be shifted.

Sample program

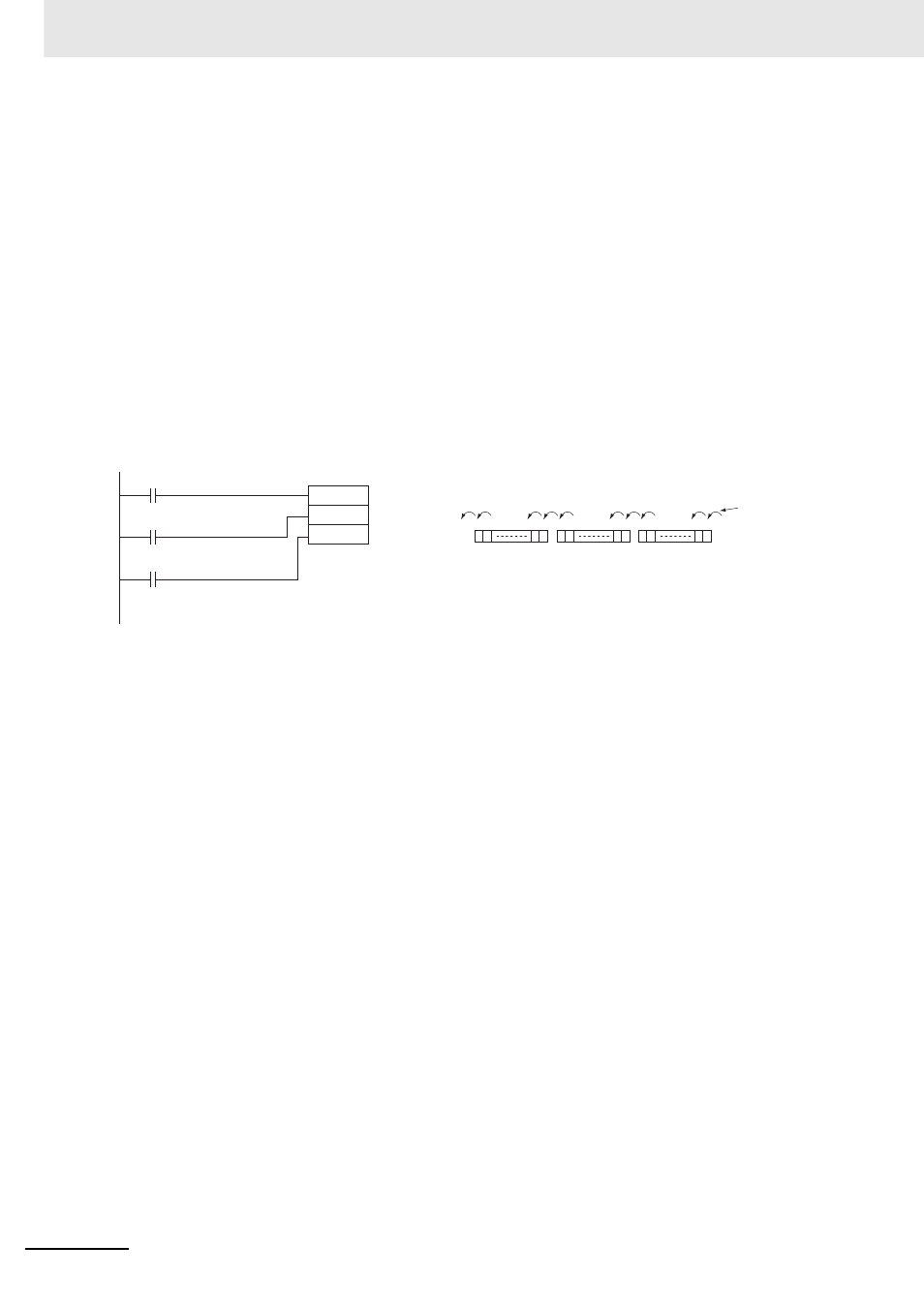

Shift Register Exceeding 16 Bits

The following example shows a 48-bit shift register using words CIO 128 to CIO 130. A 1-s clock pulse

is used so that the execution condition produced by CIO 0.05 is shifted into a 3-word register between

CIO 128.00 and CIO 130.15 every second.

i

SFT

128

130

0.05

0.06

1s (1-s clock)

Reset

Shift input

Data input

0

15

0

15

0

15

1

1

1

14

14

14

E: 130CH

129CH

128CH

Lost

Contents of

0.05

St+1:

St: