2 instructions, Parity, Examples of di – Omron SYSMAC CP CP1E-N@@D@-@ User Manual

Page 240

2 Instructions

2-204

CP1E CPU Unit Instructions Reference Manual(W483)

Parity

It is possible to specify the parity of the ASCII data for use in error control during data transmissions.

The leftmost bit of each ASCII character will be automatically adjusted for even, odd, or no parity.

• When no parity (0) is designated, the leftmost bit will always be zero. When even parity (1) is desig-

nated, the leftmost bit will be adjusted so that the total number of ON bits is even. When odd parity (2)

is designated, the leftmost bit of each ASCII character will be adjusted so that there is an odd number

of ON bits. The status of the parity bit does not affect the meaning of the ASCII code.

• Examples of even parity:

When adjusted for even parity, ASCII “31” (00110001) will be “B1” (10110001: parity bit turned ON to

create an even number of ON bits); ASCII “36” (00110110) will be “36” (00110110: parity bit remains

OFF because the number of ON bits is already even).

• Examples of odd parity:

When adjusted for odd parity, ASCII “36” (00110110) will be “B6” (10110110: parity bit turned ON to

create an odd number of ON bits); ASCII “46” (01000110) will be “46” (01000110: parity bit remains

OFF because the number of ON bits is already odd).

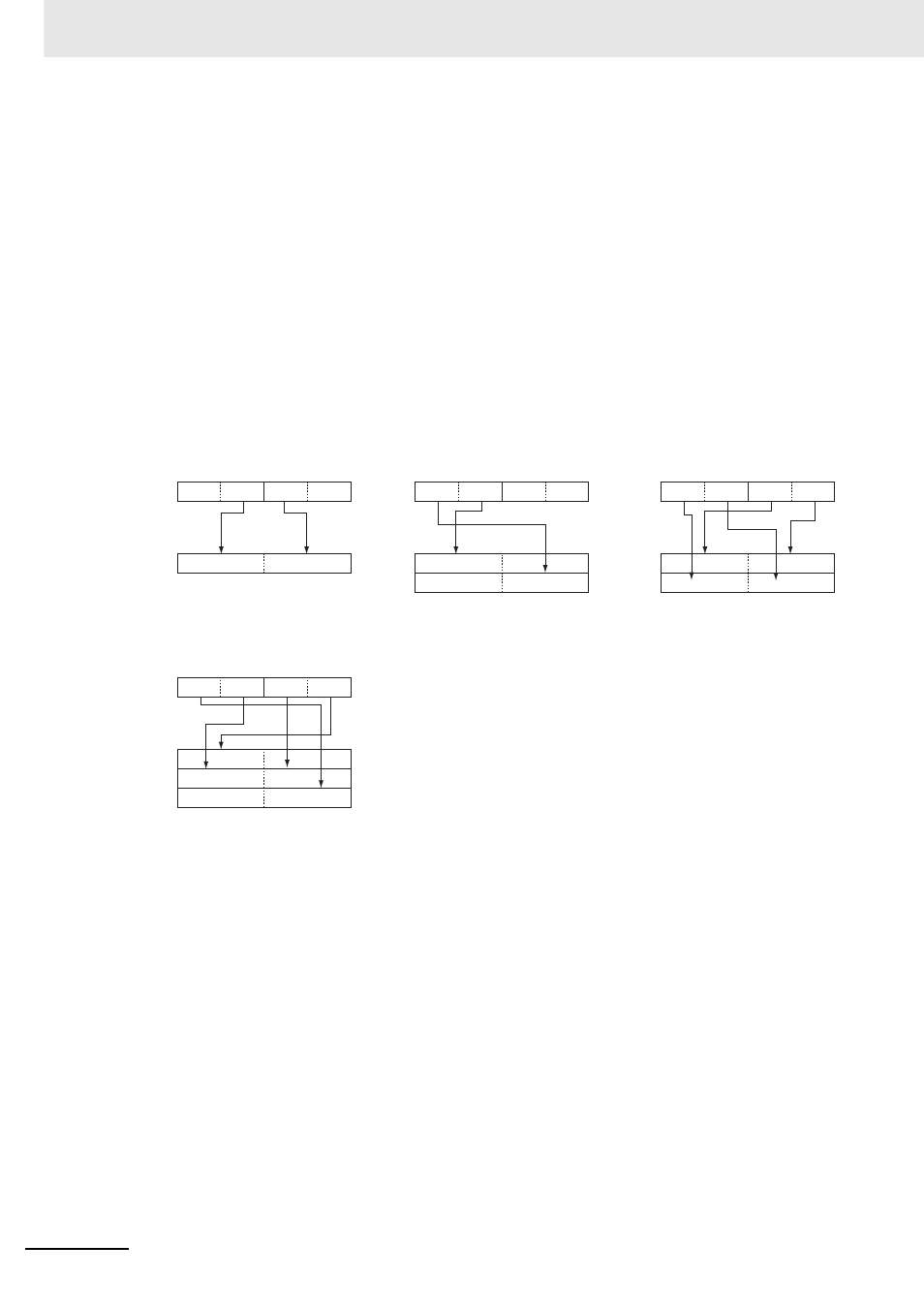

Examples of Di

Di: #0011

Di: #0112

Di: #0030

Di: #0130

Digit 3

Digit 2

Digit 1

Digit 0

Leftmost

Rightmost

Digit 3

Digit 2

Digit 1

Digit 0

Digit 3

Digit 2

Digit 1

Digit 0

Leftmost

Rightmost

Leftmost

Rightmost

Leftmost

Rightmost

Digit 3

Digit 2

Digit 1

Digit 0

Leftmost

Rightmost

Rightmost

Leftmost

D

D

D+1

S

8

11

12

15

0

3

4

7

S

8

11

12

15

0

3

4

7

D

D+1

S

8

11

12

15

0

3

4

7

8

15

0

7

8

15

0

7

8

15

0

7

D

D+1

D+2

S

8

11

12

15

0

3

4

7

8

15

0

7