Rainbow Electronics ATtiny861_V User Manual

Page 64

64

2588B–AVR–11/06

ATtiny261/461/861

and

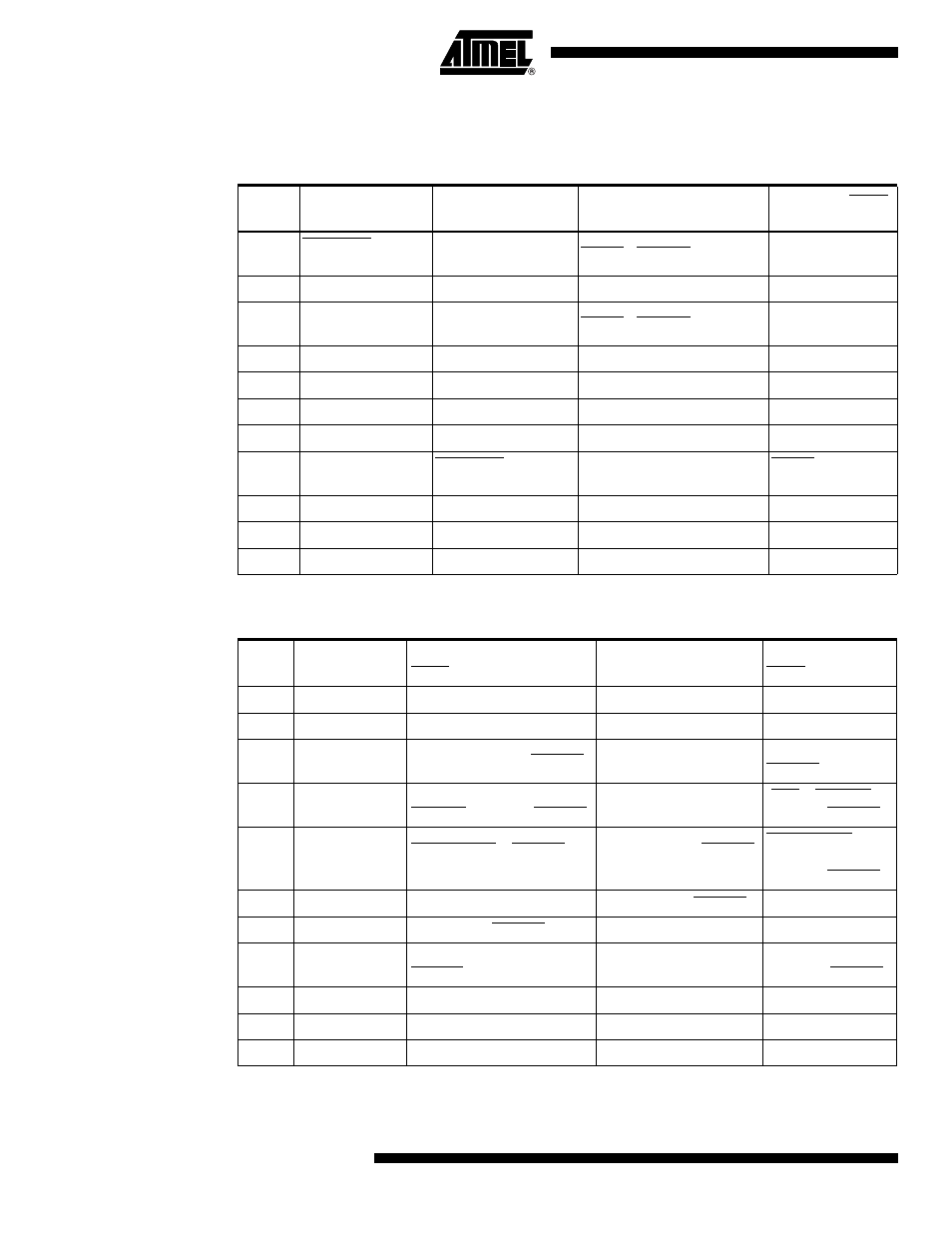

Table 12-5

relate the alternate functions of Port B to the overriding signals

shown in

Figure 12-5 on page 59

.

Note:

1. 1 when the Fuse is “0” (Programmed).

Note:

1. INTRC means that one of the internal RC Oscillators are selected (by the CKSEL fuses),

EXTCK means that external clock is selected (by the CKSEL fuses).

Table 12-4.

Overriding Signals for Alternate Functions in PB7..PB4

Signal

Name

PB7/RESET/dW/

ADC10/PCINT15

PB6/ADC9/T0/INT0/

PCINT14

PB5/XTAL2/CLKO/

OC1D/ADC8/PCINT13

(1)

PB4/XTAL1/OC1D/

ADC7/PCINT12

(1)

PUOE

RSTDISBL

(1)

•

DWEN

(1)

0

INTRC • EXTCLK

INTRC

PUOV

1

0

0

0

DDOE

RSTDISBL

(1)

•

DWEN

(1)

0

INTRC • EXTCLK

INTRC

DDOV

debugWire Transmit 0

0

0

PVOE

0

0

OC1D Enable

OC1D Enable

PVOV

0

0

OC1D

OC1D

PTOE

0

0

0

0

DIEOE

0

RSTDISBL + (PCINT5

• PCIE + ADC9D)

INTRC • EXTCLK + PCINT4 •

PCIE + ADC8D

INTRC + PCINT12

• PCIE + ADC7D

DIEOV

ADC10D

ADC9D

(INTRC • EXTCLK) + ADC8D INTRC • ADC7D

DI

PCINT15

T0/INT0/PCINT14

PCINT13

PCINT12

AIO

RESET / ADC10

ADC9

XTAL2, ADC8

XTAL1, ADC7

Table 12-5.

Overriding Signals for Alternate Functions in PB3..PB0

Signal

Name

PB3/OC1B/

PCINT11

PB2/SCK/USCK/SCL/

OC1B/PCINT10

PB1/MISO/DO/OC1A/

PCINT9

PB0/MOSI/DI/SDA/

OC1A/PCINT8

PUOE

0

0

0

0

PUOV

0

0

0

0

DDOE

0

USI_TWO_WIRE • USIPOS

0

USI_TWO_WIRE •

USIPOS

DDOV

0

(USI_SCL_HOLD +

PORTB2) • DDB2 • USIPOS

0

(SDA + PORTB0) •

DDRB0 • USIPOS

PVOE

OC1B Enable

OC1B Enable + USIPOS •

USI_TWO_WIRE • DDRB2

OC1A Enable + USIPOS

• USI_THREE_WIRE

OC1A Enable +

(USI_TWO_WIRE •

DDRB0 • USIPOS)

PVOV

OC1B

OC1B

OC1A + (DO • USIPOS)

OC1A

PTOE

0

USI_PTOE • USIPOS

0

0

DIEOE PCINT11 • PCIE

PCINT10 • PCIE + USISIE •

USIPOS

PCINT9 • PCIE

PCINT8 • PCIE +

(USISIE • USIPOS)

DIEOV

0

0

0

0

DI

PCINT11

USCK/SCL/PCINT10

PCINT9

DI/SDA/PCINT8

AIO