2 external interrupt control register a - eicra, 1 external interrupt mask register - eimsk, 2 external interrupt control register a – eicra – Rainbow Electronics ATmega64C1 User Manual

Page 82

82

7647A–AVR–02/08

ATmega32/64/M1/C1

10.2

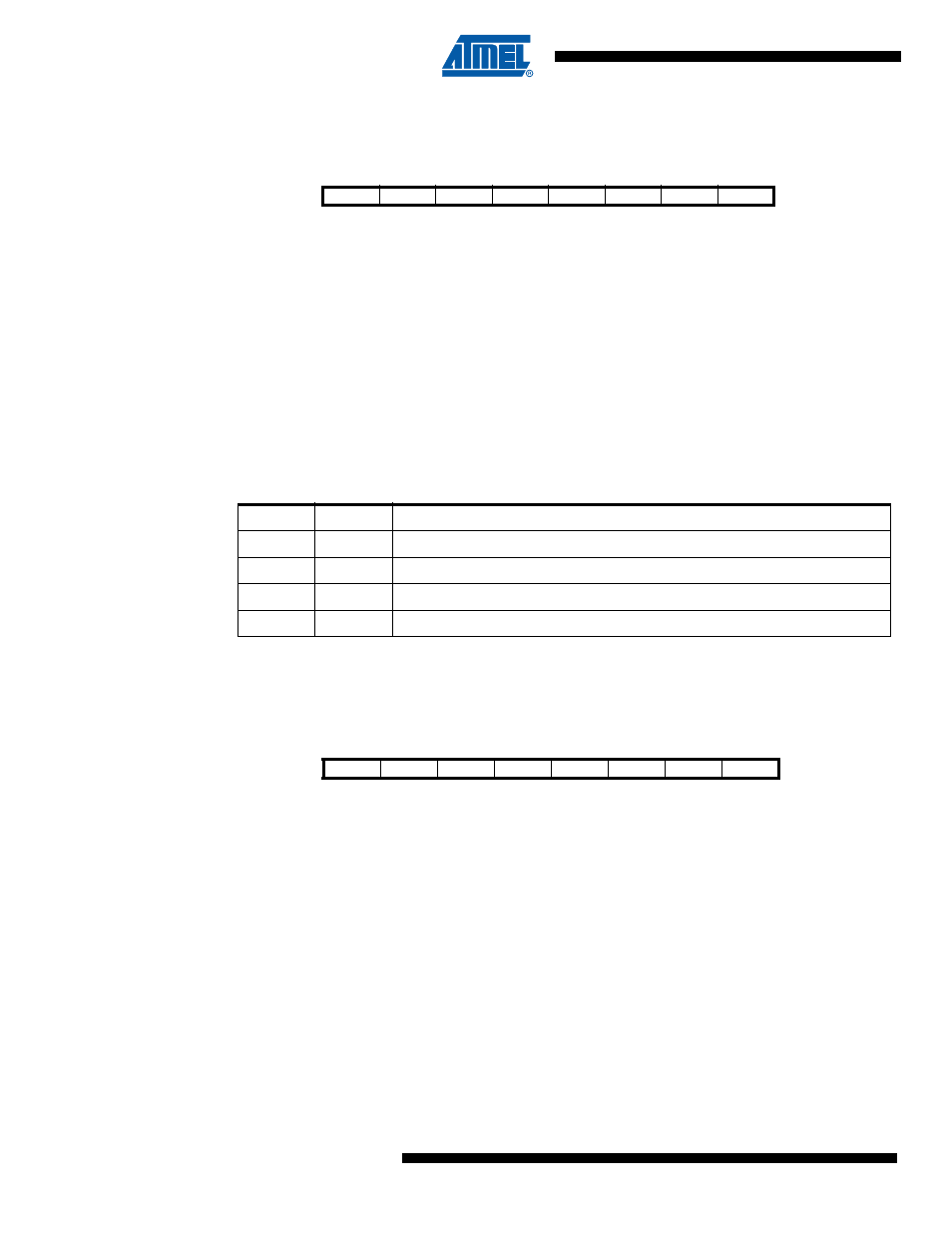

External Interrupt Control Register A – EICRA

The External Interrupt Control Register A contains control bits for interrupt sense control.

• Bit 7..0 – ISC31, ISC30 - ISC01, ISC00: Interrupt Sense Control 0 Bit 1 and Bit 0

The External Interrupts 3 - 0 are activated by the external pins INT3:0 if the SREG I-flag and the

corresponding interrupt mask in the EIMSK is set. The level and edges on the external pins that

activate the interrupt are defined in

. Edges on INT3..INT0 are registered asynchro-

nously. The value on the INT3:0 pins are sampled before detecting edges. If edge or toggle

interrupt is selected, pulses that last longer than one clock period will generate an interrupt.

Shorter pulses are not guaranteed to generate an interrupt. Observe that CPU clock frequency

can be lower than XTAL frequency if the XTAL divider is enabled. If low level interrupt is

selected, the low level must be held until the completion of the currently executing instruction to

generate an interrupt. If enabled, a level triggered interrupt will generate an interrupt request as

long as the pin is held low.

Note:

1. n = 3, 2, 1 or 0.

When changing the ISCn1/ISCn0 bits, the interrupt must be disabled by clearing its Interrupt

Enable bit in the EIMSK Register. Otherwise an interrupt can occur when the bits are changed.

10.2.1

External Interrupt Mask Register – EIMSK

• Bit 7..4 – Res: Reserved Bits

These bits are unused bits in the ATmega32/64/M1/C1, and will always read as zero.

• Bit 3..0 – INT3 - 0: External Interrupt Request 3:0 Enable

When an INT3 – INT0 bit is written to one and the I-bit in the Status Register (SREG) is set

(one), the corresponding external pin interrupt is enabled. The Interrupt Sense Control bits in the

External Interrupt Control Register A - EICRA defines whether the external interrupt is activated

on rising or falling edge or level sensed. Activity on any of these pins will trigger an interrupt

request even if the pin is enabled as an output. This provides a way of generating a software

interrupt.

Bit

7

6

5

4

3

2

1

0

ISC31

ISC30

ISC21

ISC20

ISC11

ISC10

ISC01

ISC00

EICRA

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0

Table 10-1.

Interrupt Sense Control

(1)

ISCn1

ISCn0

Description

0

0

The low level of INTn generates an interrupt request.

0

1

Any logical change on INTn generates an interrupt request.

1

0

The falling edge between two samples of INTn generates an interrupt request.

1

1

The rising edge between two samples of INTn generates an interrupt request.

Bit

7

6

5

4

3

2

1

0

–

–

–

–

INT3

INT2

INT1

INT0

EIMSK

Read/Write

R

R

R

R

R

R

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0