3 offset compensation schemes, 4 adc accuracy definitions – Rainbow Electronics ATmega64C1 User Manual

Page 236

236

7647A–AVR–02/08

ATmega32/64/M1/C1

18.6.3

Offset Compensation Schemes

The gain stage has a built-in offset cancellation circuitry that nulls the offset of differential mea-

surements as much as possible. The remaining offset in the analog path can be measured

directly by shortening both differential inputs using the AMPxIS bit with both inputs unconnected.

(

See “Amplifier 0 Control and Status register – AMP0CSR” on page 251.

trol and Status register – AMP1CSR” on page 252.

See “Amplifier 1 Control and Status

register – AMP1CSR” on page 252.

). This offset residue can be then subtracted in software from

the measurement results. Using this kind of software based offset correction, offset on any chan-

nel can be reduced below one LSB.

18.6.4

ADC Accuracy Definitions

An n-bit single-ended ADC converts a voltage linearly between GND and V

REF

in 2

n

steps

(LSBs). The lowest code is read as 0, and the highest code is read as 2

n

-1.

Several parameters describe the deviation from the ideal behavior:

•

Offset: The deviation of the first transition (0x000 to 0x001) compared to the ideal transition

(at 0.5 LSB). Ideal value: 0 LSB.

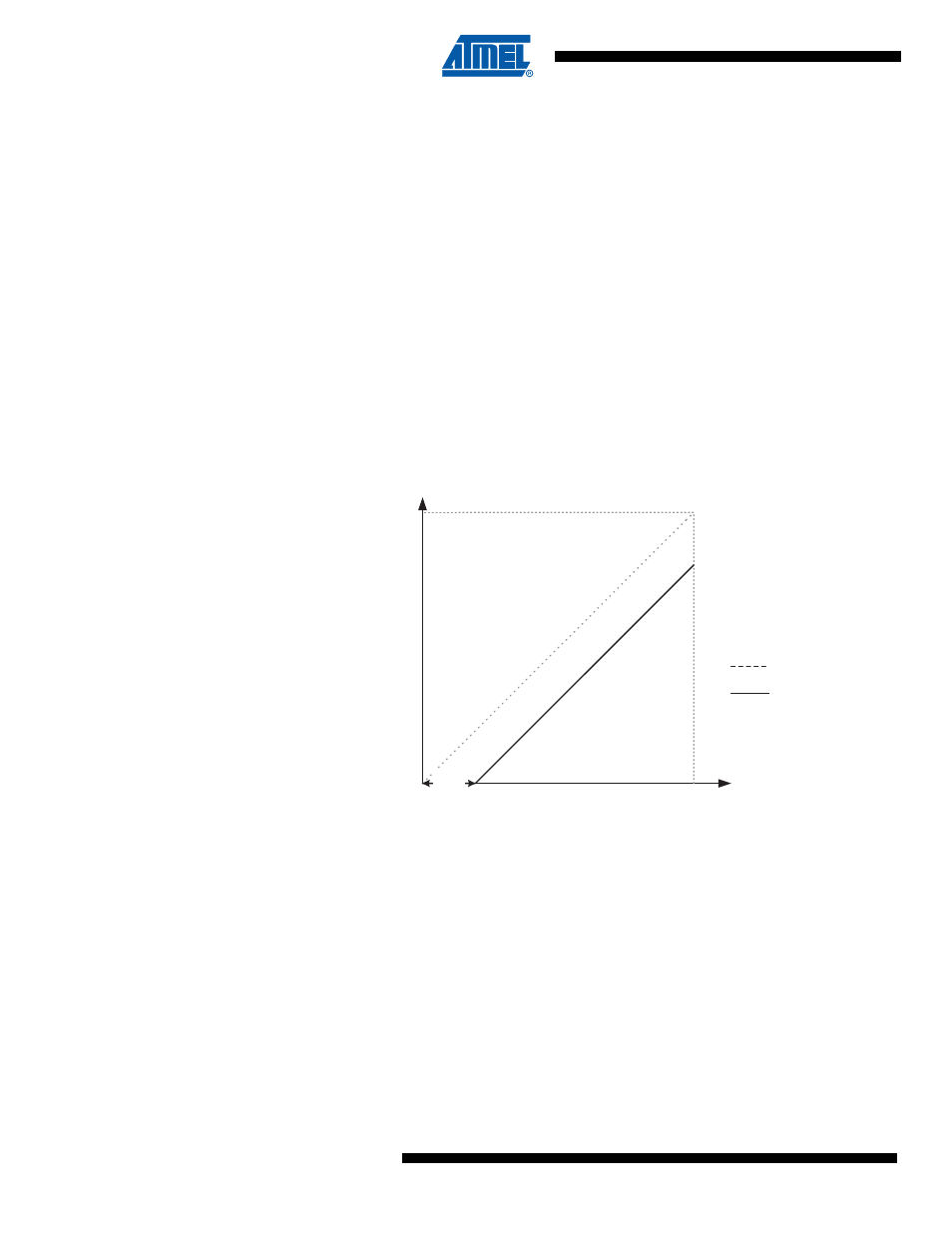

Figure 18-10. Offset Error

•

Gain Error: After adjusting for offset, the Gain Error is found as the deviation of the last

transition (0x3FE to 0x3FF) compared to the ideal transition (at 1.5 LSB below maximum).

Ideal value: 0 LSB

Output Code

V

REF

Input Voltage

Ideal ADC

Actual ADC

Offset

Error