6 update of values – Rainbow Electronics ATmega64C1 User Manual

Page 140

140

7647A–AVR–02/08

ATmega32/64/M1/C1

PSC Cycle = 2 * (POCRnRBH/L + 1) * 1/Fclkpsc

Note:

Minimal value for PSC Cycle = 2 * 1/Fclkpsc

Note that in center aligned mode, POCRnRAH/L is not required (as it is in one-ramp mode) to

control PSC Output waveform timing. This allows POCRnRAH/L to be freely used to adjust ADC

synchronization (

See “Analog Synchronization” on page 148.

).

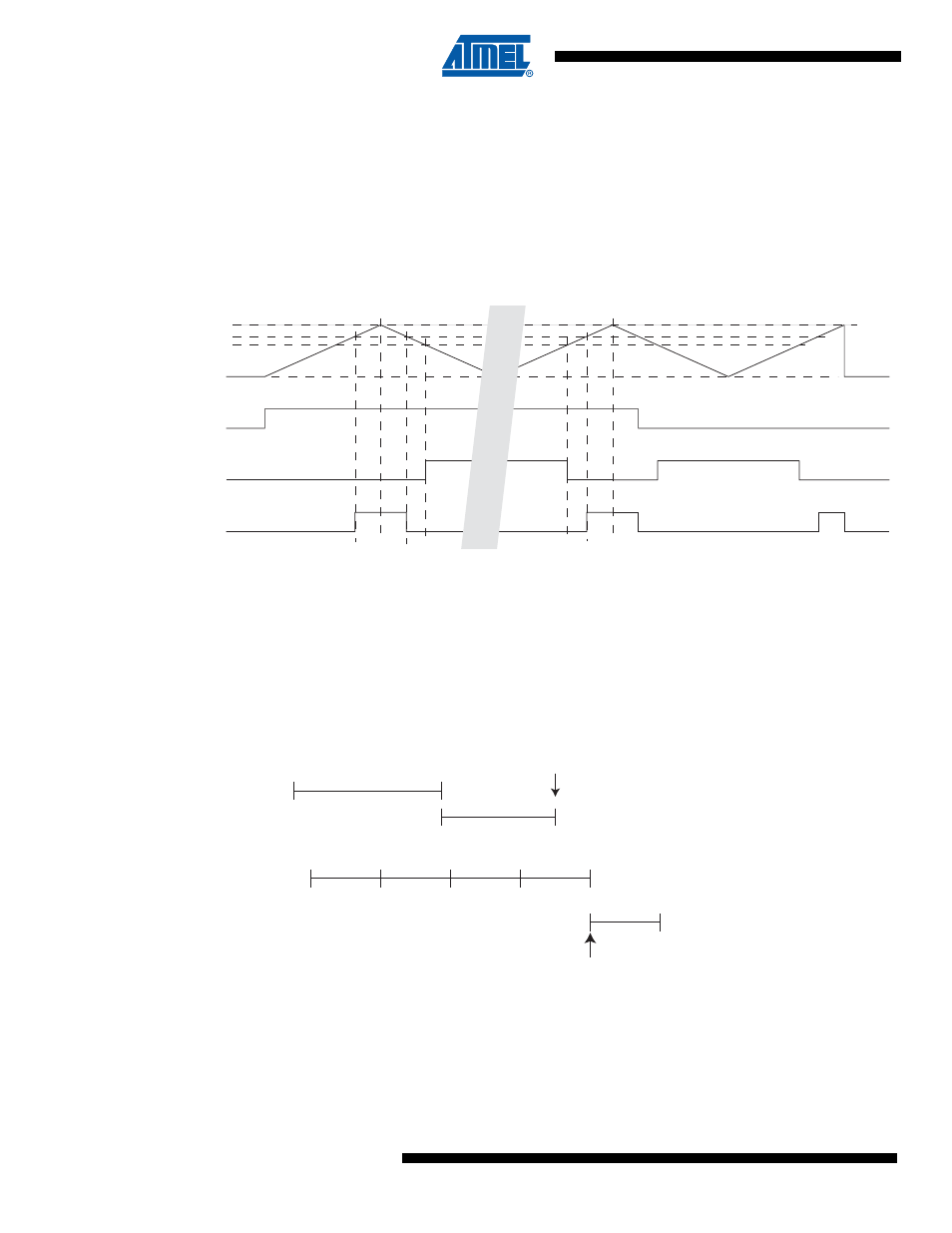

Figure 14-7. Controlled Start and Stop Mechanism in Centered Mode

Note:

See “PSC Control Register – PCTL” on page 153.

14.6

Update of Values

To avoid unasynchronous and incoherent values in a cycle, if an update of one of several values

is necessary, all values are updated at the same time at the end of the cycle by the PSC. The

new set of values is calculated by sofware and the update is initiated by software.

Figure 14-8. Update at the end of complete PSC cycle.

The software can stop the cycle before the end to update the values and restart a new PSC

cycle.

PSCOUTnA

PSCOUTnB

PSC Counter

POCRnRB

POCRnSA

POCRnSB

0

Run

Software

PSC

Regulation Loop

Calculation

Writting in

PSC Registers

Cycle

With Set i

Cycle

With Set i

Cycle

With Set i

Cycle

With Set i

Cycle

With Set j

End of Cycle

Request for

an Update