Rainbow Electronics ATmega64C1 User Manual

Page 231

231

7647A–AVR–02/08

ATmega32/64/M1/C1

When initiating a single ended conversion by setting the ADSC bit in ADCSRA, the conversion

starts at the following rising edge of the ADC clock cycle. See

“Changing Channel or Reference

for details on differential conversion timing.

A normal conversion takes 13 ADC clock cycles. The first conversion after the ADC is switched

on (ADEN in ADCSRA is set) takes 25 ADC clock cycles in order to initialize the analog circuitry.

The actual sample-and-hold takes place 3.5 ADC clock cycles after the start of a normal conver-

sion and 13.5 ADC clock cycles after the start of an first conversion. When a conversion is

complete, the result is written to the ADC Data Registers, and ADIF is set. In Single Conversion

mode, ADSC is cleared simultaneously. The software may then set ADSC again, and a new

conversion will be initiated on the first rising ADC clock edge.

When Auto Triggering is used, the prescaler is reset when the trigger event occurs. This assures

a fixed delay from the trigger event to the start of conversion. In this mode, the sample-and-hold

takes place two ADC clock cycles after the rising edge on the trigger source signal. Three addi-

tional CPU clock cycles are used for synchronization logic.

In Free Running mode, a new conversion will be started immediately after the conversion com-

pletes, while ADSC remains high. For a summary of conversion times, see

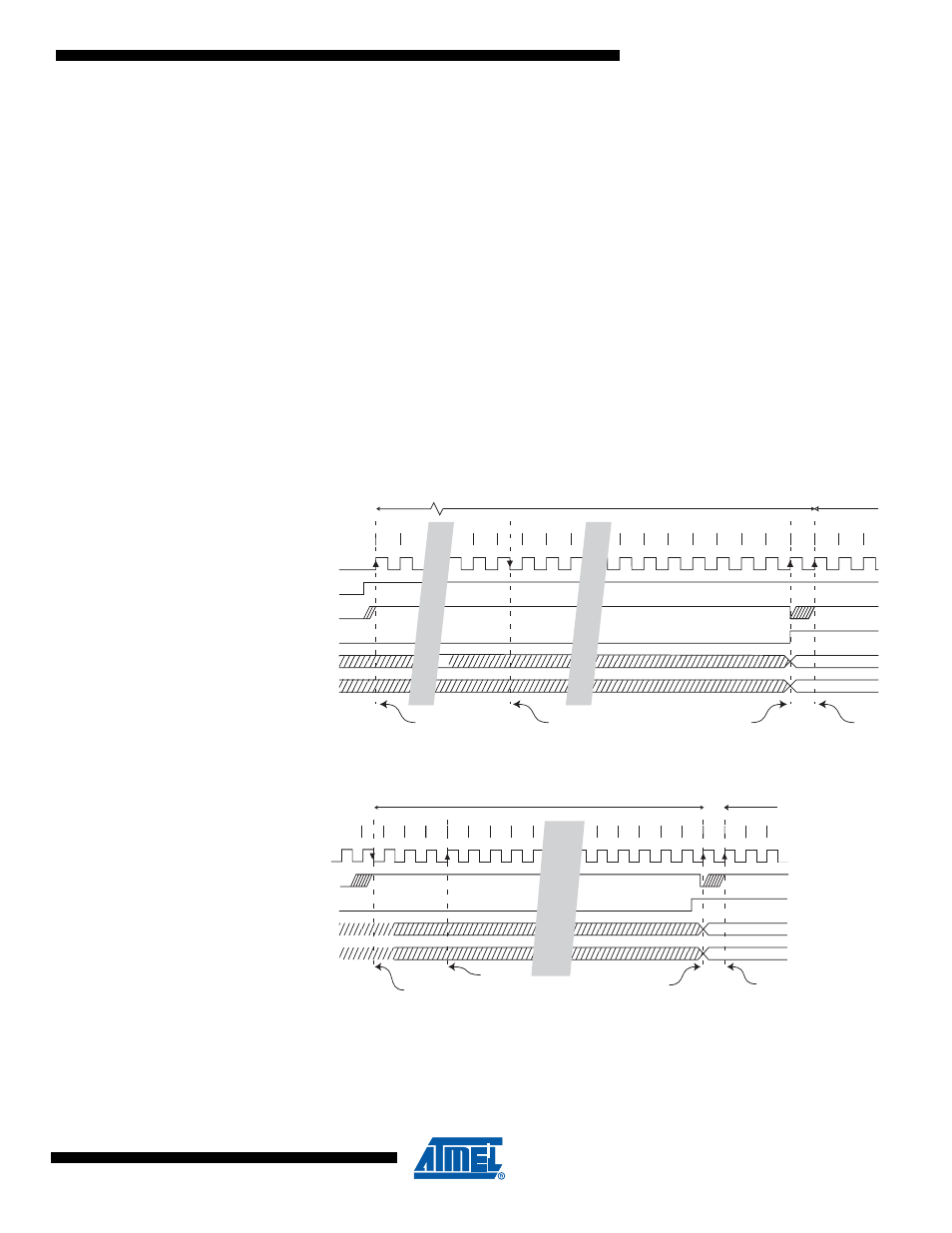

Figure 18-4. ADC Timing Diagram, First Conversion (Single Conversion Mode)

Figure 18-5. ADC Timing Diagram, Single Conversion

Sign and MSB of Result

LSB of Result

ADC Clock

ADSC

Sample & Hold

ADIF

ADCH

ADCL

Cycle Number

ADEN

1

2

12

13

14

15

16

22

23

24

25

26

27

28

1

2

First Conversion

Next

Conversion

3

MUX and REFS

Update

MUX

and REFS

Update

Conversion

Complete

4

5

6

7

8

10

11

12

13

14

Sign and MSB of Result

LSB of Result

ADC Clock

ADSC

ADIF

ADCH

ADCL

Cycle Number

1

2

One Conversion

Next Conversion

3

Sample & Hold

MUX and REFS

Update

Conversion

Complete

MUX and REFS

Update

1

2

3