Rainbow Electronics ATmega64C1 User Manual

Page 76

76

7647A–AVR–02/08

ATmega32/64/M1/C1

MISO_A: Master Data input, Slave Data output pin for SPI channel. When the SPI is enabled as

a master, this pin is configured as an input regardless of the setting of DDD2. When the SPI is

enabled as a slave, the data direction of this pin is controlled by DDD2. When the pin is forced to

be an input, the pull-up can still be controlled by the PORTD2 bit.

PCINT18, Pin Change Interrupt 18.

• PCINT17/PSCIN0/CLKO – Bit 1

PCSIN0, PSC Digital Input 0.

CLKO, Divided System Clock: The divided system clock can be output on this pin. The divided

system clock will be output if the CKOUT Fuse is programmed, regardless of the PORTD1 and

DDD1 settings. It will also be output during reset.

PCINT17, Pin Change Interrupt 17.

• PCINT16/PSCOUT0A – Bit 0

PSCOUT0A: Output 0 of PSC 0.

PCINT16, Pin Change Interrupt 16.

and

relates the alternate functions of Port D to the overriding signals

Table 9-10.

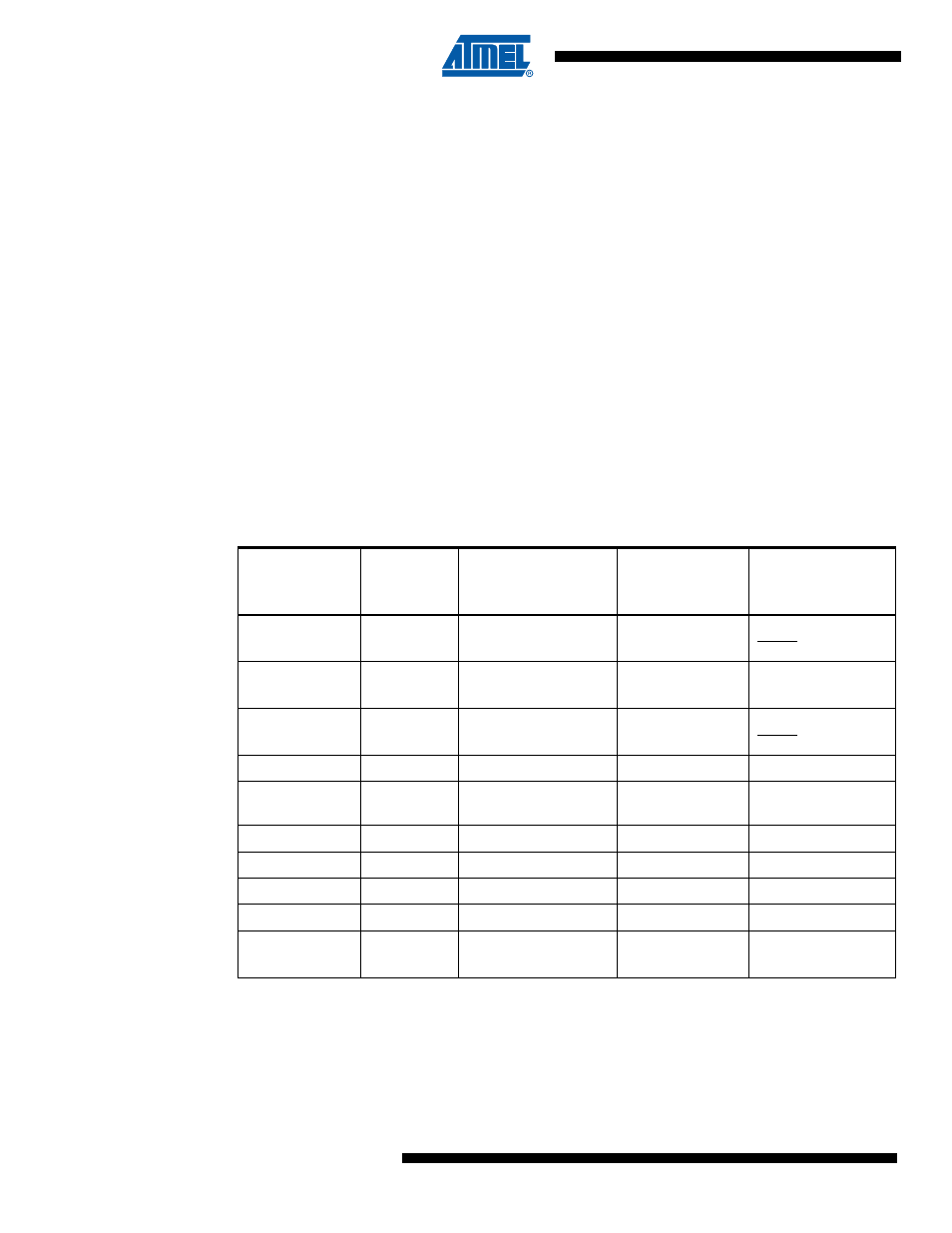

Overriding Signals for Alternate Functions PD7..PD4

Signal Name

PD7/

ACMP0/

PCINT23

PD6/ADC3/

ACMPN2/INT0/

PCINT22

PD5/ADC2/

ACMP2/PCINT21

PD4/ADC1/RXD/

RXLIN/ICP1A/

SCK_A/PCINT20

PUOE

0

0

0

RXEN + SPE •

MSTR • SPIPS

PUOV

0

0

0

PD4 •

PUD

DDOE

0

0

0

RXEN + SPE •

MSTR • SPIPS

DDOV

0

0

0

0

PVOE

0

0

0

SPE • MSTR •

SPIPS

PVOV

0

0

0

–

DIEOE

ACMP0D

ADC3D + In0en

ADC2D

ADC1D

DIEOV

0

In0en

0

0

DI

–

INT0

ICP1A

AIO

ACOMP0

ADC3

ACMPM

ADC2

ACOMP2

ADC1