Rainbow Electronics W90N745CDG User Manual

Page 66

W90N745CD/W90N745CDG

Publication Release Date: September 22, 2006

-

61

-

Revision

A2

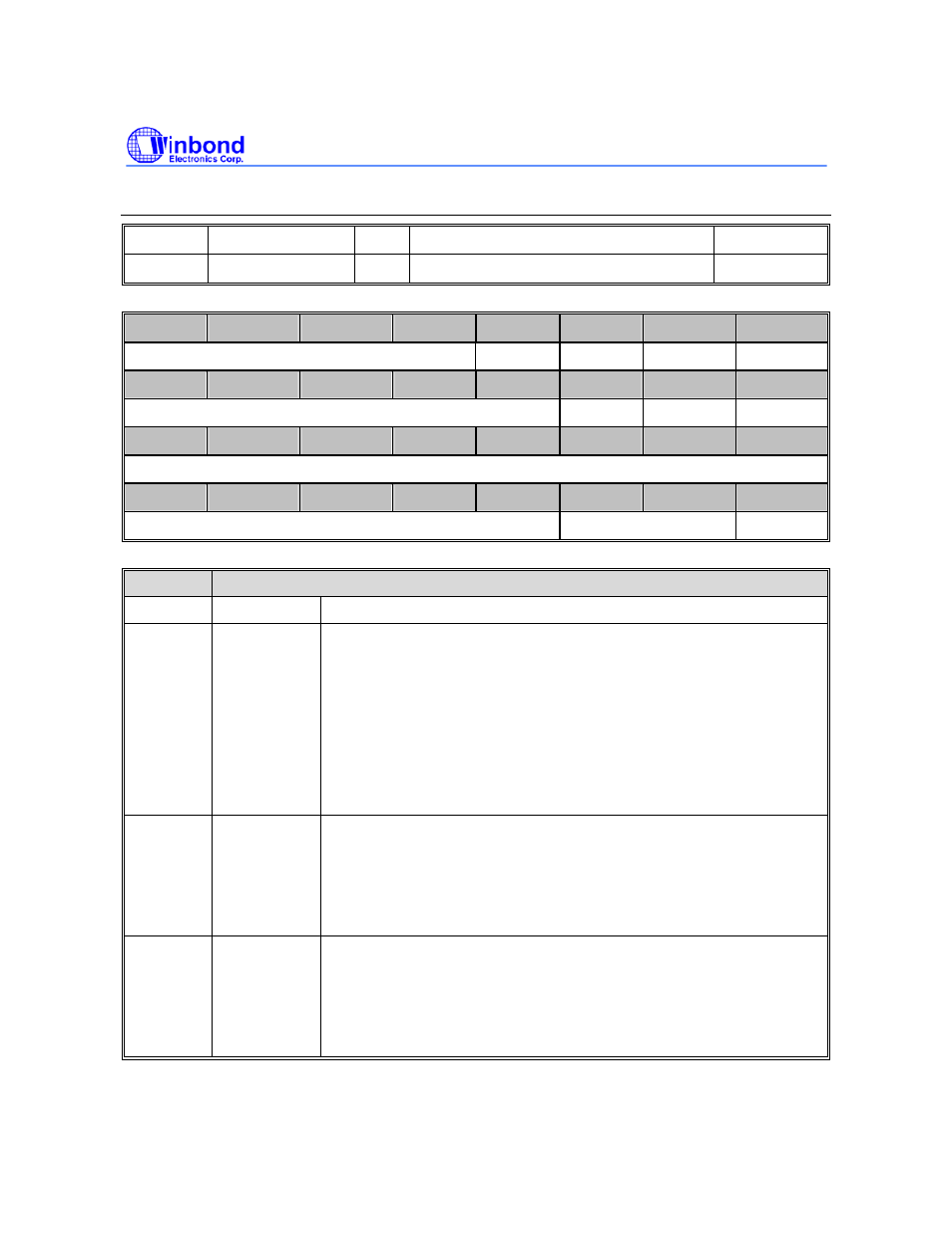

EBI Control Register (EBICON)

REGISTER ADDRESS R/W

DESCRIPTION

RESET

VALUE

EBICON

0xFFF0_1000

R/W EBI control register

0x0001_0000

31

30

29

28

27

26

25

24

RESERVED EXBE3

EXBE2 EXBE1 EXBE0

23

22

21

20

19

18

17

16

RESERVED REFEN

REFMOD

CLKEN

15

14

13

12

11

10

9

8

REFRAT

7

6

5

4

3

2

1

0

REFRAT WAITVT

LITTLE

BITS

DESCRIPTION

[31:27] RESERVED

[27] EXBE3

External IO bank 3 byte enable

This function is used for some devices that with high and low bytes

enable signals to control which byte will be write or mask data output

when read. For this kind device, software can set this bit HIGH to

implement this function. Detail pin interconnection is showed as Figure

6.3.8.

1 = nWBE[1:0] pin is byte enable signals, nWE will be used as write

strobe signal to SRAM.

0 = nWBE[1:0] pin is byte write strobe signal.

[26] EXBE2

External IO bank 2 byte enable

The bit function description is the same as EXBE3 above.

1 = nWBE[1:0] pin is byte enable signals, nWE will be used as write

strobe signal to SRAM.

0 = nWBE[1:0] pin is byte write strobe signal.

[25] EXBE1

External IO bank 1 byte enable

The bit function description is the same as EXBE3 above.

1 = nWBE[1:0] pin is byte enable signals, nWE will be used as write

strobe signal to SRAM

0 = nWBE[1:0] pin is byte write strobe signal