Rainbow Electronics W90N745CDG User Manual

Page 289

W90N745CD/W90N745CDG

- 284 -

Continued.

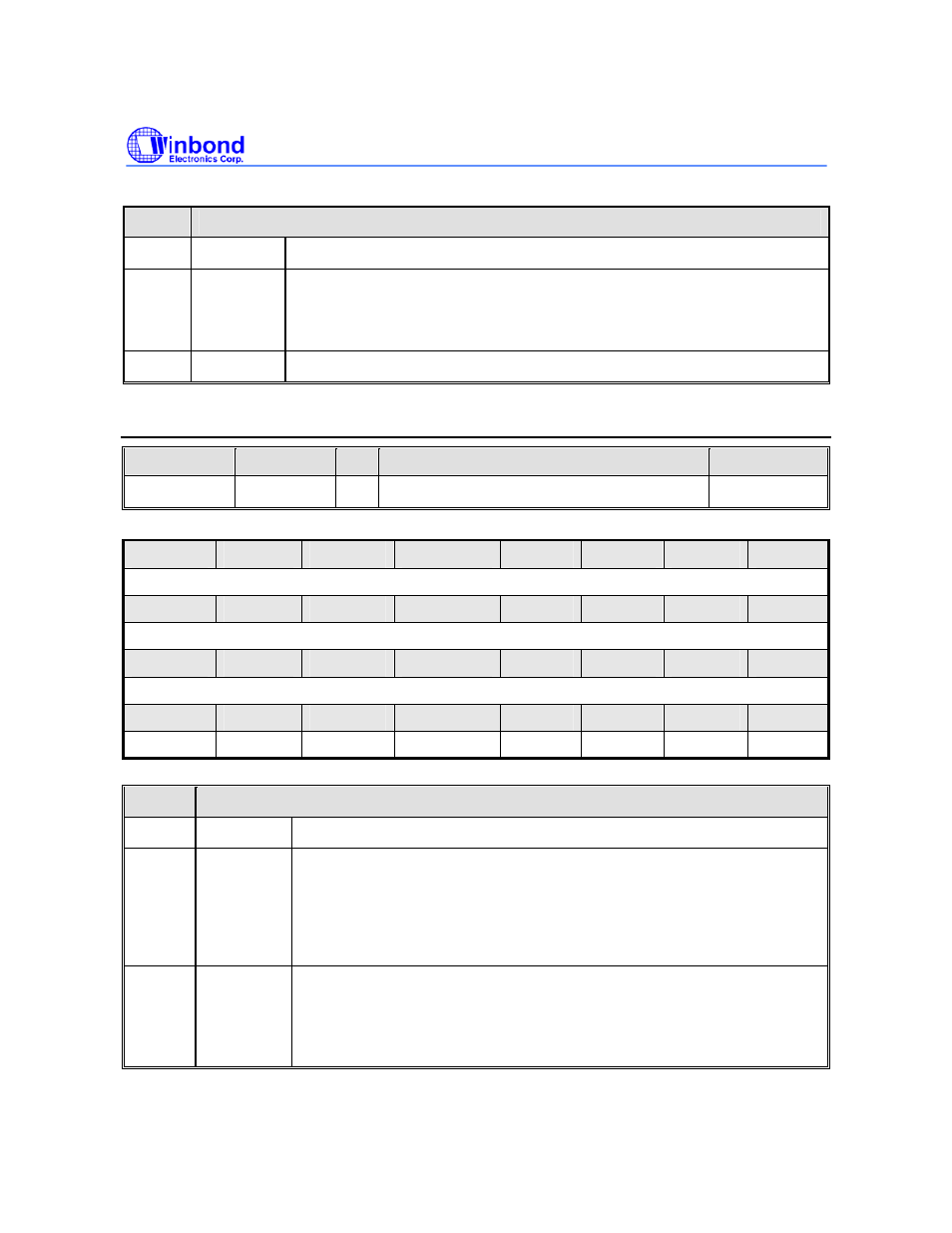

BITS

DESCRIPTIONS

[3:2]

Reserved -

[1]

RTS#

Complement version of RTS# (Request-To-Send) signal

Writing 0x00 to MCR, RTS# bit are set to logic 1’s;

Writing 0x0f to MCR, RTS# bit are reset to logic 0’s.

[0]

Reserved -

HSUART Line Status Control Register (HSUART_LSR)

REGISTER

OFFSET

R/W

DESCRIPTION

RESET VALUE

HSUART_LSR

0x14

R

Line Status Register

0x6060_6060

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved

7

6

5

4

3

2

1

0

ERR_RX TE THRE

BII

FEI PEI OEI RFDR

BITS

DESCRIPTIONS

[31:8]

Reserved

[7]

ERR_RX

RX FIFO Error

0 = RX FIFO works normally

1 = There is at least one parity error (PE), framing error (FE), or break

indication (BI) in the FIFO. ERR_RX is cleared when CPU reads the

LSR and if there are no subsequent errors in the RX FIFO.

[6]

TE

Transmitter Empty

0 = Either Transmitter Holding Register (THR - TX FIFO) or Transmitter

Shift Register (TSR) are not empty.

1 = Both THR and TSR are empty.