Rainbow Electronics W90N745CDG User Manual

Page 127

W90N745CD/W90N745CDG

- 122 -

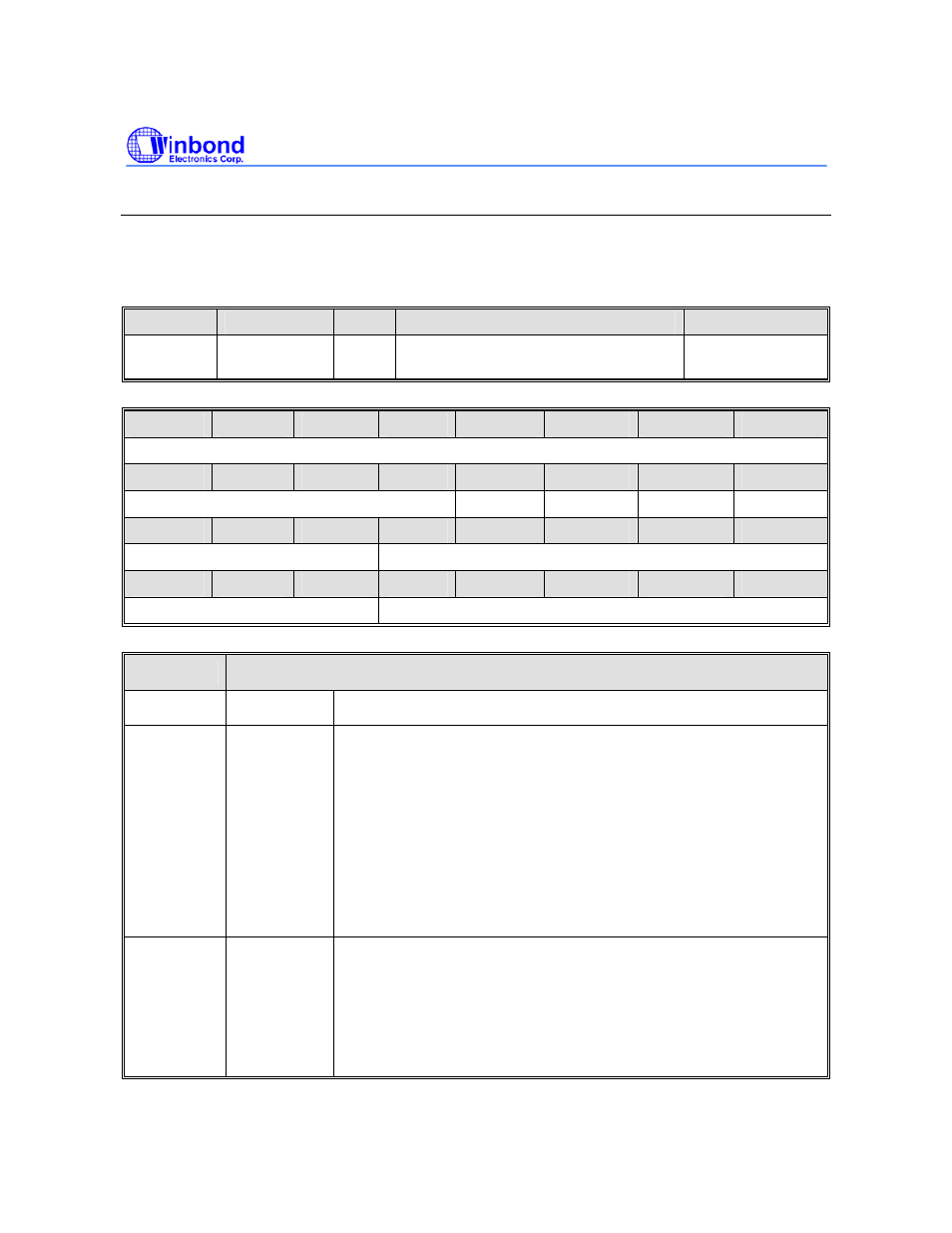

MII Management Control and Address Register (MIIDA)

The EMC provides MII management function to access the control and status registers of the external

PHY. The MIIDA register is used to keep the MII management command information, like the register

address, external PHY address, MDC clocking rate, read/write etc.

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET VALUE

MIIDA 0xFFF0_3098

R/W

MII Management Control and Address

Register

0x0090_0000

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

MDCCR MDCON

PreSP

BUSY

Write

15

14

13

12

11

10

9

8

Reserved PHYAD

7

6

5

4

3

2

1

0

Reserved PHYRAD

BITS

DESCRIPTIONS

[31:24] Reserved

-

[23:20] MDCCR

The MDC Clock Rating controls the MDC clock rating for MII

Management I/F.

Depend on the IEEE Std. 802.3 clause 22.2.2.11, the minimum

period for MDC shall be 400ns. In other words, the maximum

frequency for MDC is 2.5MHz. The MDC is divided from the AHB bus

clock, the HCLK. Consequently, for different HCLKs the different

ratios are required to generate appropriate MDC clock.

The following table shows relationship between HCLK and MDC

clock in different MDCCR configurations. The T

HCLK

indicates the

period of HCLK.

[19] MDC

The MDC Clock ON Always controls the MDC clock generation. If the

MDCON is set to high, the MDC clock actives always. Otherwise, the

MDC will only active while S/W issues a MII management command.

1’b0: The MDC clock will only active while S/W issues a MII

management command.

1’b1: The MDC clock actives always.