Rainbow Electronics W90N745CDG User Manual

Page 36

W90N745CD/W90N745CDG

Publication Release Date: September 22, 2006

-

31

-

Revision

A2

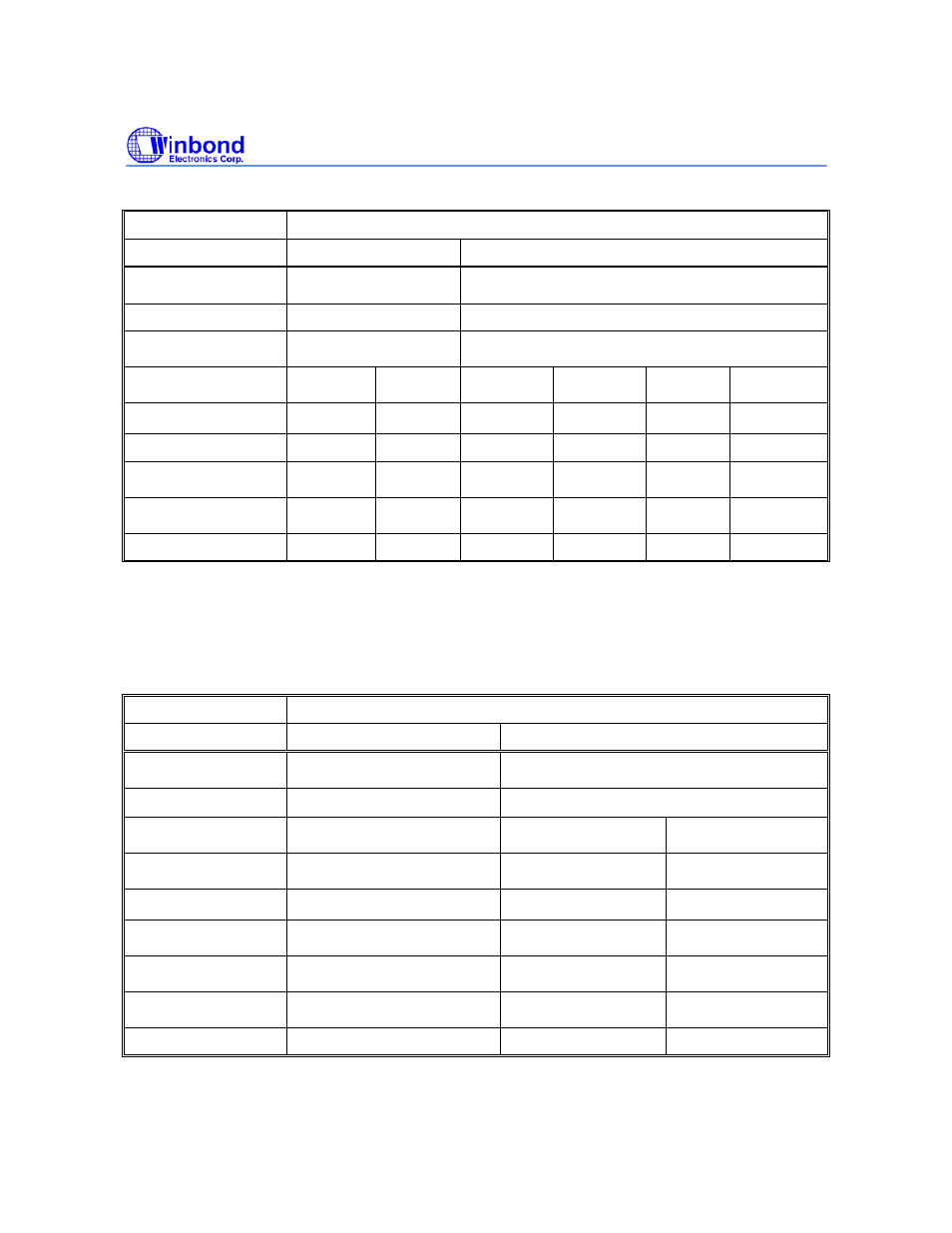

Table 6.2.4 Word access read operation with Big Endian

ACCESS OPERATION

READ OPERATION (CPU REGISTER Í EXTERNAL MEMORY)

XD WIDTH

HALF WORD

BYTE

Bit Number

CPU Reg Data

31 0

CDAB

31 0

DCBA

SA

WA WA

Bit Number

SD

31 0

CD AB

31 0

D C B A

Bit Number

ED

31 0

CD XX

31 0

CD AB

31 0

D X X X

31 0

D C X X

31 0

D C B X

31 0

D C B A

XA

WA WA+2 WA WA+1 WA+2 WA+3

SDQM [1-0]

AA AA XA XA XA XA

Bit Number

XD

15 0

CD

15 0

AB

7 0

D

7 0

C

7 0

B

7 0

A

Bit Number

Ext. Mem Data

15 0

CD

15 0

AB

7 0

D

7 0

C

7 0

B

7 0

A

Timing Sequence

1st read

2

nd

read

1st read

2nd read

3rd read

4th read

Table 6.2.5 and Table 6.2.6

Using big-endian and half-word access, Program/Data path between register and external memory.

HA = Address whose LSB is 0,2,4,6,8,A,C,E

X = Don’t care

nWBE [1-0] / SDQM [1-0] = A means active and U means inactive

Table 6.2.5 Half-word access write operation with Big Endian

ACCESS OPERATION

WRITE OPERATION (CPU REGISTER Î EXTERNAL MEMORY)

XD WIDTH

HALF WORD

BYTE

Bit Number

CPU Reg Data

31 0

ABCD

31 0

ABCD

SA

HA HA

Bit Number

SD

31 0

CD CD

31 0

CD CD

31 0

CD CD

Bit Number

ED

31 0

CD CD

7 0

C

7 0

D

XA

HA HA

HA+1

nWBE [1-0] /

SDQM [1-0]

AA XA

XA

Bit Number

XD

15 0

CD

7 0

C

7 0

D

Bit Number

Ext. Mem Data

15 0

CD

7 0

C

7 0

D

Timing Sequence

1st write

2nd write