Rainbow Electronics W90N745CDG User Manual

Page 292

W90N745CD/W90N745CDG

Publication Release Date: September 22, 2006

-

287

-

Revision

A2

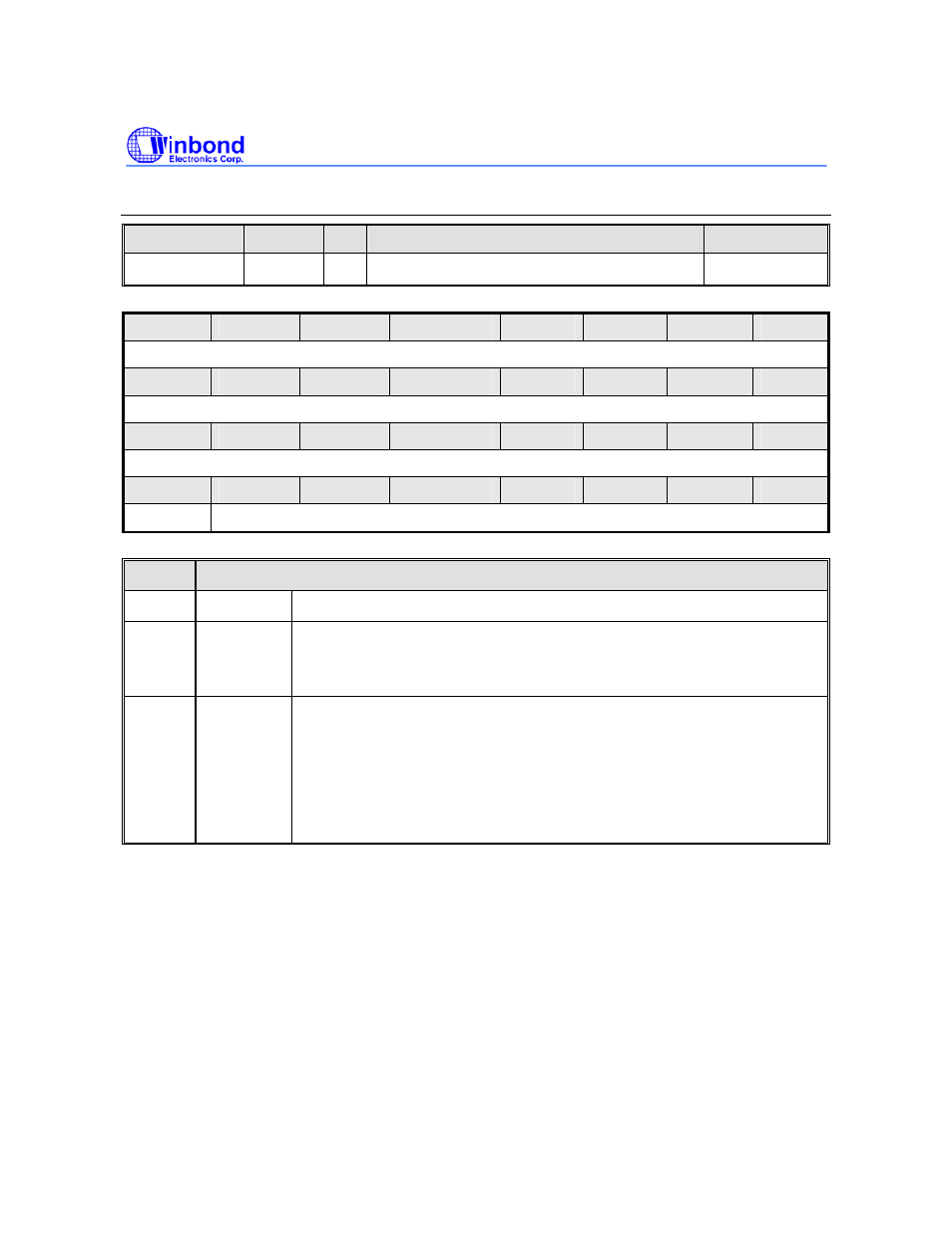

HSUART Time Out Register (HSUART_TOR)

REGISTER

OFFSET R/W

DESCRIPTION

RESET VALUE

HSUART_TOR

0x1C

R/W

Time Out Register

0x0000_0000

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved

7

6

5

4

3

2

1

0

TOIE TOIC

BITS

DESCRIPTIONS

[31:8]

Reserved -

[7]

TOIE

Time Out Interrupt Enable

The feature of receiver time out interrupt is enabled only when TOR [7] =

IER[0] = 1.

[6:0]

TOIC

Time Out Interrupt Comparator

The time out counter resets and starts counting (the counting clock = baud

rate) whenever the RX FIFO receives a new data word. Once the content

of time out counter (TOUT_CNT) is equal to that of time out interrupt

comparator (TOIC), a receiver time out interrupt (Irpt_TOUT) is generated if

TOR [7] = IER [0] = 1. A new incoming data word or RX FIFO empty clears

Irpt_TOUT.

- MAX5151 (16 pages)

- MAXQ3108 (64 pages)

- MAX5661 (39 pages)

- MAX6691 (7 pages)

- MAX5362 (12 pages)

- ADC10158 (26 pages)

- MAX8922L (14 pages)

- MAX8596Z (8 pages)

- MAX7491 (18 pages)

- MAX15040 (15 pages)

- MAX5177 (16 pages)

- ADC08138 (22 pages)

- MAX5961 (42 pages)

- T89C51RD2 (86 pages)

- MAX16055 (9 pages)

- MAX6659 (17 pages)

- ADC0820 (20 pages)

- MAX6678 (19 pages)

- MAX8884Z (15 pages)

- MAX16915 (9 pages)

- MAX8620 (18 pages)

- MAX5144 (12 pages)

- MAX6670 (8 pages)

- MAX8760 (39 pages)

- W78C32C (14 pages)

- MX7533 (8 pages)

- MAX8727 (13 pages)

- MAX9053 (15 pages)

- W78C54 (16 pages)

- MAX8614B (15 pages)

- W90N740 (219 pages)

- MAX6626 (13 pages)

- ADC10738 (30 pages)

- MAX17000 (31 pages)

- MAX5051 (21 pages)

- MAXQ1004 (18 pages)

- MAX6871 (51 pages)

- MX7847 (12 pages)

- MAX6608 (6 pages)

- MAX17083 (15 pages)

- MAX6641 (17 pages)

- MAX5251 (16 pages)

- MAX6338 (8 pages)

- MAX6690 (16 pages)

- MAX8668 (18 pages)