Rainbow Electronics W90N745CDG User Manual

Page 282

W90N745CD/W90N745CDG

Publication Release Date: September 22, 2006

-

277

-

Revision

A2

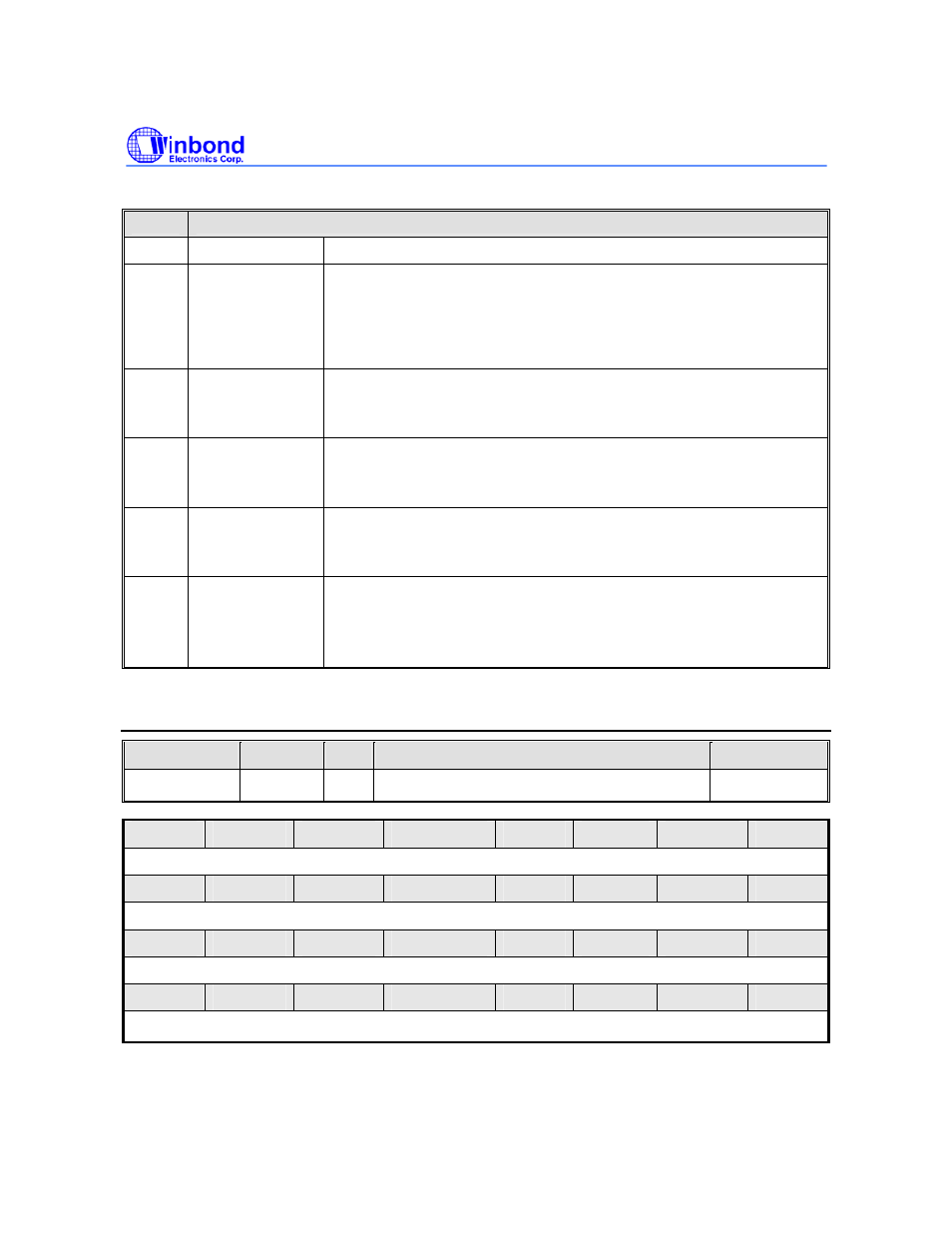

BITS

DESCRIPTIONS

[31:5]

Reserved -

[4]

nDBGACK_EN

ICE debug mode acknowledge enable

0 = When DBGACK is high, the UART receiver time-out clock will be

held

1 = No matter what DBGACK is high or not, the UART receiver timer-

out clock will not be held

[3]

MSIE

MODEM Status Interrupt (Irpt_MOS) Enable

0 = Mask off Irpt_MOS

1 = Enable Irpt_MOS

[2]

RLSIE

Receive Line Status Interrupt (Irpt_RLS) Enable

0 = Mask off Irpt_RLS

1 = Enable Irpt_RLS

[1]

THREIE

Transmit Holding Register Empty Interrupt (Irpt_THRE) Enable

0 = Mask off Irpt_THRE

1 = Enable Irpt_THRE

[0]

RDAIE

Receive Data Available Interrupt (Irpt_RDA) Enable and

Time-out Interrupt (Irpt_TOUT) Enable

0 = Mask off Irpt_RDA and Irpt_TOUT

1 = Enable Irpt_RDA and Irpt_TOUT

HSUART Divider Latch (Low Byte) Register (HSUART_DLL)

REGISTER

OFFSET

R/W

DESCRIPTION

RESET VALUE

HSUART_DLL

0x00

R/W

Divisor Latch Register (LS) (DLAB = 1)

0x0000_0000

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved

7

6

5

4

3

2

1

0

Baud Rate Divider (Low Byte)