Rainbow Electronics W90N745CDG User Manual

Page 361

W90N745CD/W90N745CDG

Publication Release Date: September 22, 2006

-

357

-

Revision

A2

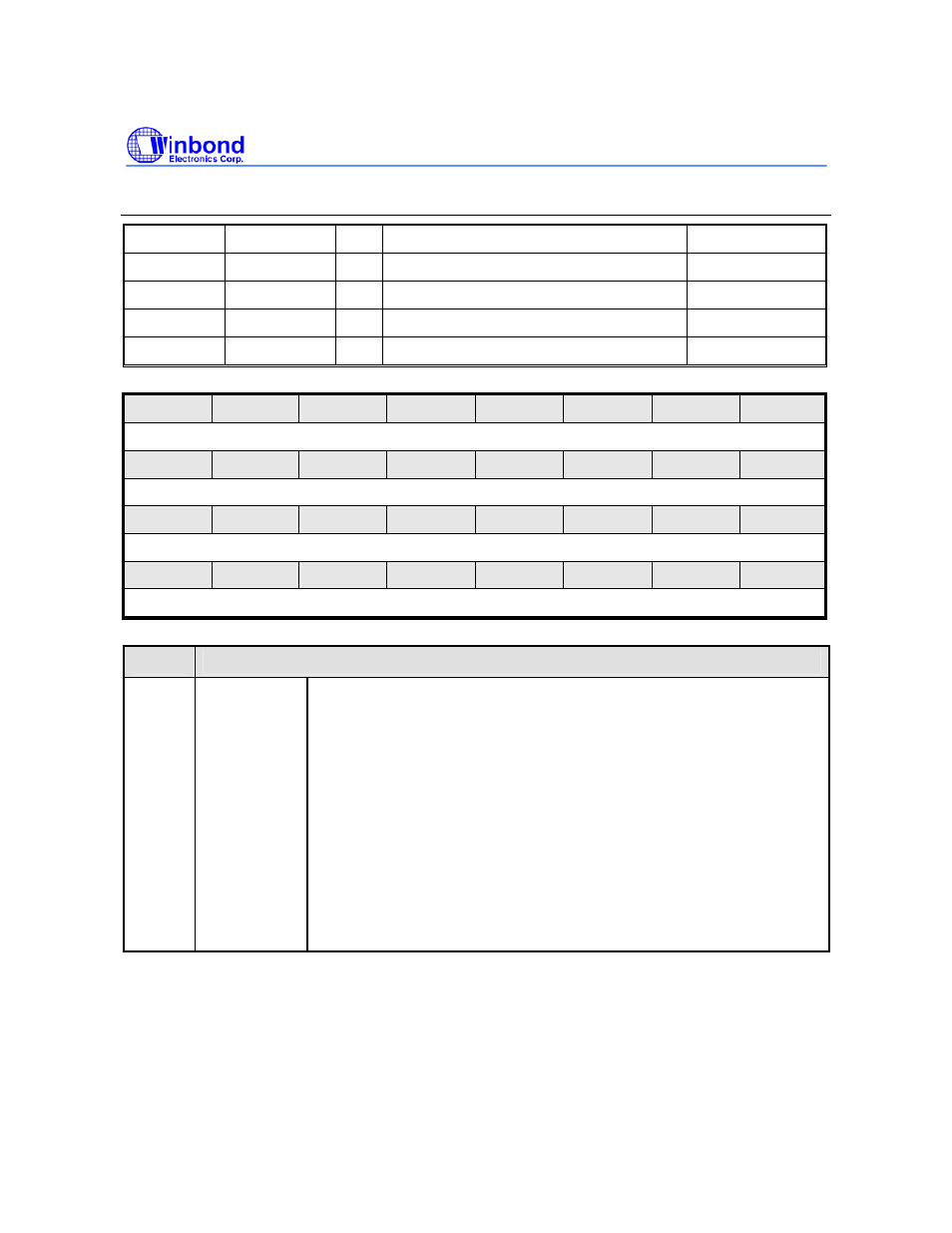

Data Transmit Register 0/1/2/3 (Tx0/1/2/3)

REGISTER ADDRESS R/W

DESCRIPTION

RESET

VALUE

USI_TX0

0xFFF8_6210

W

USI Data Transmit Register 0

0x0000_0000

USI_TX1

0xFFF8_6214

W

USI Data Transmit Register 1

0x0000_0000

USI_TX2

0xFFF8_6218

W

USI Data Transmit Register 2

0x0000_0000

USI_TX3

0xFFF8_621C

W

USI Data Transmit Register 3

0x0000_0000

31

30

29

28

27

26

25

24

Tx

[31:24]

23

22

21

20

19

18

17

16

Tx

[23:16]

15

14

13

12

11

10

9

8

Tx

[15:8]

7

6

5

4

3

2

1

0

Tx

[7:0]

BITS

DESCRIPTIONS

[31:0]

Tx

Data Transmit Register

The Data Transmit Registers hold the data to be transmitted in the next

transfer. Valid bits depend on the transmit bit length field in the CNTRL

register. For example, if CNTRL[Tx_BIT_LEN] is set to 0x08 and the

CNTRL[Tx_NUM] is set to 0x0, the bit Tx0[7:0] will be transmitted in next

transfer. If CNTRL[Tx_BIT_LEN] is set to 0x00 and CNTRL[Tx_NUM] is

set to 0x3, the core will perform four 32-bit transmit/receive successive

using the same setting (the order is Tx0[31:0], Tx1[31:0], Tx2[31:0],

Tx3[31:0]).

NOTE: The RxX and TxX registers share the same flip-flops, which

means that what is received from the input data line in one transfer will

be transmitted on the output data line in the next transfer if no write

access to the TxX register is executed between the transfers.