Rainbow Electronics W90N745CDG User Manual

Page 280

W90N745CD/W90N745CDG

Publication Release Date: September 22, 2006

-

275

-

Revision

A2

Continued.

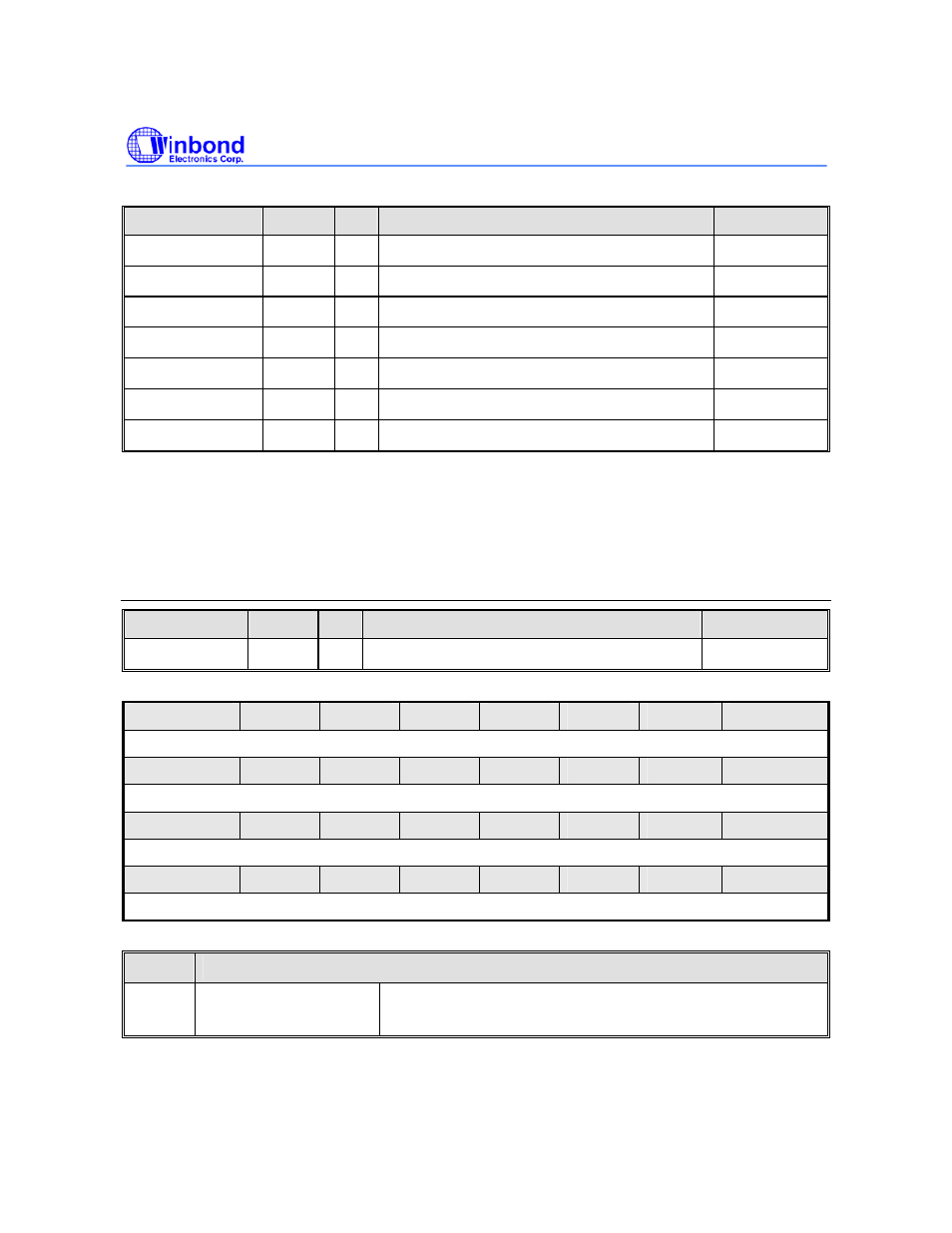

REGISTER

OFFSET R/W

DESCRIPTION

RESET VALUE

HSUART_IIR 0x08

R

Interrupt

Identification Register

0x8181_8181

HSUART_FCR 0x08

W

FIFO

Control Register

Undefined

HSUART_LCR 0x0C

R/W

Line

Control Register

0x0000_0000

HSUART_MCR 0x10

R/W

Modem Control Register (Optional)

0x0000_0000

HSUART_LSR 0x14

R Line Status Register

0x6060_6060

HSUART_MSR 0x18

R MODEM Status Register (Optional)

0x0000_0000

HSUART_TOR 0x1C

R/W Time Out Register

0x0000_0000

Note: Real register address = 0xFFF8_0000+ (UART number – 1) * (0x0100) + offset

NOTE: All of these registers are implemented 8-bit in UART design and it will be repeated 4 times

before send to APB bus. For example, when ARM CPU read register UART1_BRR, ARM CPU will get

UART1_RBR = {RBR[7:0], _RBR[7:0], RBR[7:0], RBR[7:0]}.

HSUART Receive Buffer Register (HSUART_RBR)

REGISTER

OFFSET R/W

DESCRIPTION

RESET VALUE

HSUART_RBR

0x00

R

Receive Buffer Register (DLAB = 0)

Undefined

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved

7

6

5

4

3

2

1

0

8-bit Received Data

BITS

DESCRIPTIONS

[7:0]

8-bit Received Data

By reading this register, the UART will return an 8-bit data

received from SIN pin (LSB first).