Rainbow Electronics W90N745CDG User Manual

Page 167

W90N745CD/W90N745CDG

- 162 -

Continued

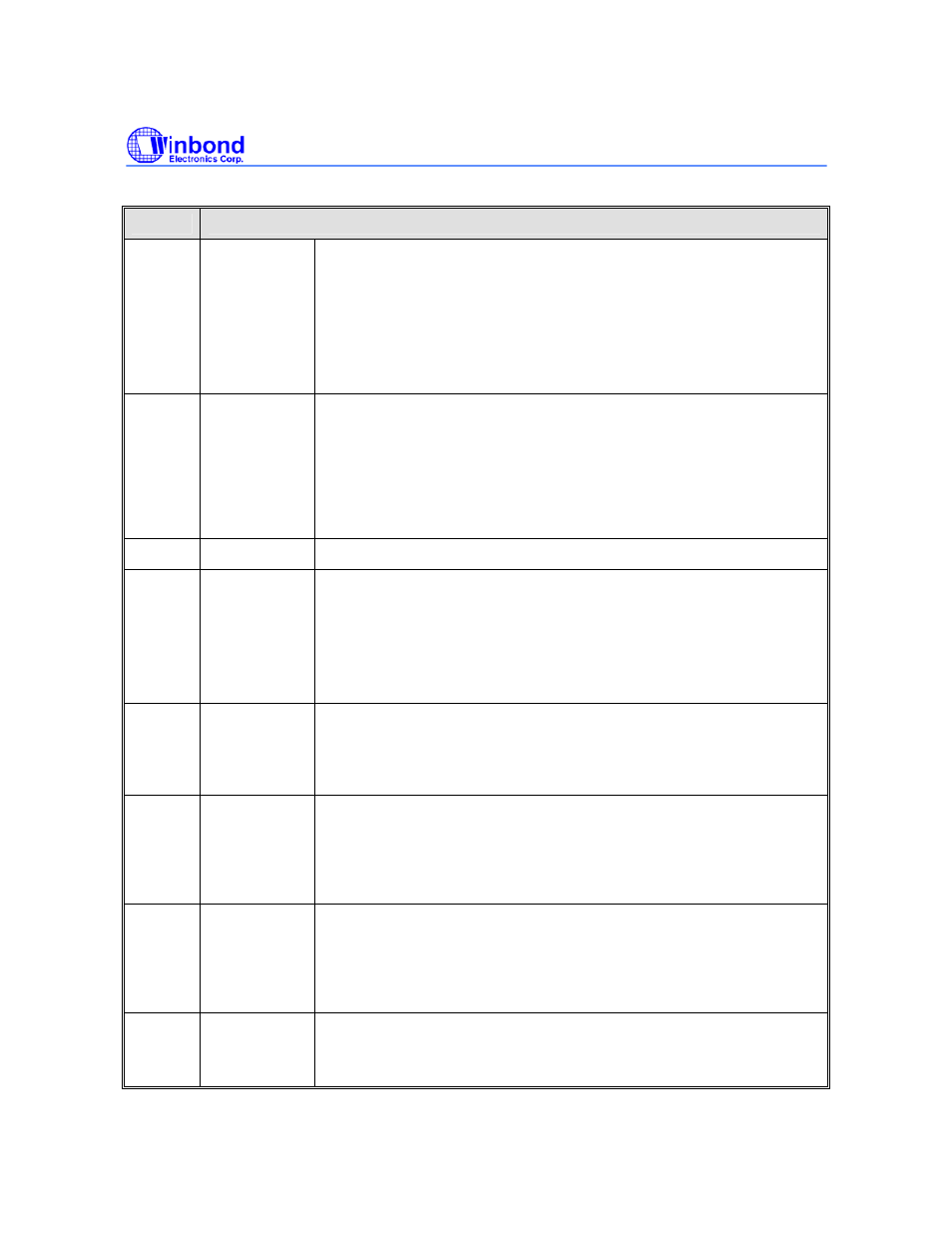

BITS

DESCRIPTIONS

[13:12] TWS

Transfer Width Select

00 = One byte (8 bits) is transferred for every GDMA operation

01 = One half-word (16 bits) is transferred for every GDMA operation

10 = One word (32 bits) is transferred for every GDMA operation

11 = Reserved

The GDMA_SCRB and GDMA_DSTB should be alignment under the

TWS selection

[11] SBMS

Single/Block Mode Select

1’b0 = Selects single mode. It requires an external GDMA request for

every incurring GDMA operation.

1’b1 = Selects block mode. It requires a single external GDMA request

during the atomic GDMA operation. An atomic GDMA operation is defined

as the sequence of GDMA operations until the transfer count register

reaches zero.

[10] Reserved

-

[9] BME

Burst Mode Enable

1’b0 = Disables the 4-data burst mode

1’b1 = Enables the 4-data burst mode

FF there are 16 words to be transferred, and BME [9]=1, the

GDMA_TCNT should be 0x04;

However, if BME [9]=0, the GDMA_TCNT should be 0x10.

[8]

SIEN

Stop Interrupt Enable

1’b0 = Do not generate an interrupt when the GDMA operation is

stopped

1’b1 = Interrupt is generated when the GDMA operation is stopped

[7] SAFIX

Source Address Fixed

1’b0 = Source address is changed during the GDMA operation

1’b1 = Do not change the destination address during the GDMA

operation. This feature can be used when data were transferred from a

single source to multiple destinations.

[6] DAFIX

Destination Address Fixed

1’b0 = Destination address is changed during the GDMA operation

1’b1 = Do not change the destination address during the GDMA

operation. This feature can be used when data were transferred from

multiple sources to a single destination.

[5] SADIR

Source Address Direction

1’b0 = Source address is incremented successively

1’b1 = Source address is decremented successively