Rainbow Electronics W90N745CDG User Manual

Page 19

W90N745CD/W90N745CDG

- 14 -

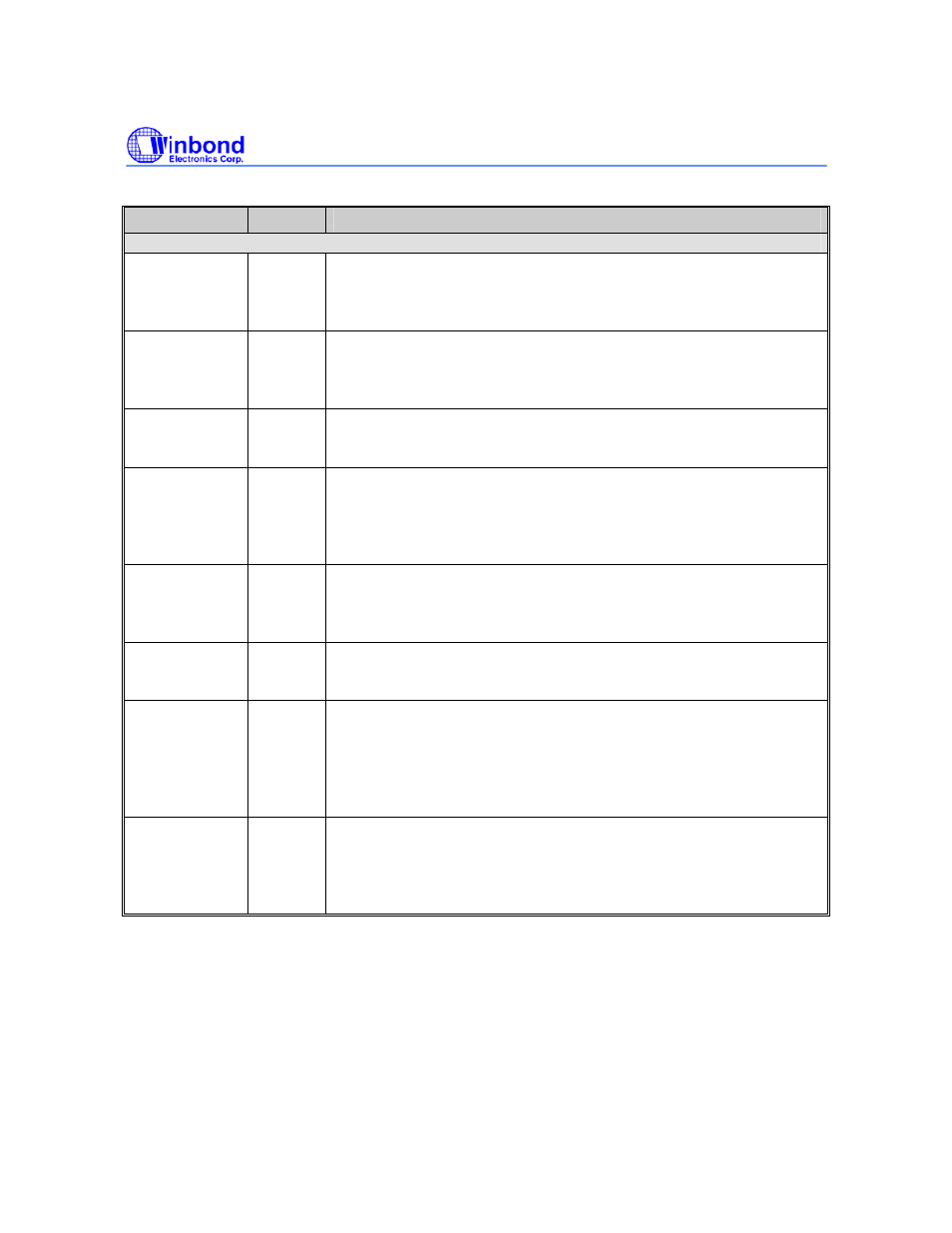

Table 5.1 W90N745 Pins Description, continued

PIN NAME

IO TYPE

DESCRIPTION

Ethernet Interface

PHY_MDC /

GPIO [29] /

KPROW [1]

IOU

RMII Management Data Clock for Ethernet. It is the reference clock of MDIO.

Each MDIO data will be latched at the rising edge of MDC clock.

General Programmable In/Out Port [29]

Keypad ROW[1] scan output.

PHY_MDIO /

GPIO [28] /

KPROW [0]

IO

RMII Management Data I/O for Ethernet. It is used to transfer RMII control and

status information between PHY and MAC.

General Programmable In/Out Port [28]

Keypad ROW[0] scan output.

PHY_TXD [1:0] /

GPIO [27:26] /

KPCOL [7:6]

IOU

2-bit Transmit Data bus for Ethernet.

General programmable In/Out Port [27:26]

Keypad column input [7:6], active low

PHY_TXEN /

GPIO [25] /

KPCOL [5]

IOU

PHY_TXEN shall be asserted synchronously with the first 2-bit of the preamble

and shall remain asserted while all di-bits to be transmitted are presented. Of

course, it is synchronized with PHY_REFCLK.

General Programmable In/Out Port [25]

Keypad column input [5], active low

PHY_REFCLK /

GPIO [24] /

KPCOL [4]

IOS

Reference Clock. The clock shall be 50MHz +/- 50 ppm with minimum 35%

duty cycle at high or low state.

General Programmable In/Out port [24]

Keypad column input [4], active low

PHY_RXD [1:0] /

GPIO [23:22] /

KPCOL [3:2]

IOS

2-bit Receive Data bus for Ethernet.

General Programmable In/Out Port [23:22]

Keypad column input [3:2], active low

PHY_CRSDV /

GPIO [21] /

KPCOL [1]

IOS

Carrier Sense / Receive Data Valid for Ethernet. The PHY_CRSDV shall be

asserted by PHY when the receive medium is non-idle. Loss of carrier shall

result in the de-assertion of PHY_CRSDV synchronous to the cycle of

PHY_REFCLK, and only on 2-bit receive data boundaries.

General Programmable In/Out port [21]

Keypad column input [1], active low

PHY_RXERR /

GPIO [20] /

KPCOL [0]

IOS

Receive Data Error for Ethernet. It indicates a data error detected by PHY.The

assertion should be lasted for longer than a period of PHY_REFCLK. When

PHY_RXERR is asserted, the MAC will report a CRC error.

General programmable In/Out port [20]

Keypad column input [0], active low