Rainbow Electronics W90N745CDG User Manual

Page 166

W90N745CD/W90N745CDG

Publication Release Date: September 22, 2006

-

161

-

Revision

A2

Continued

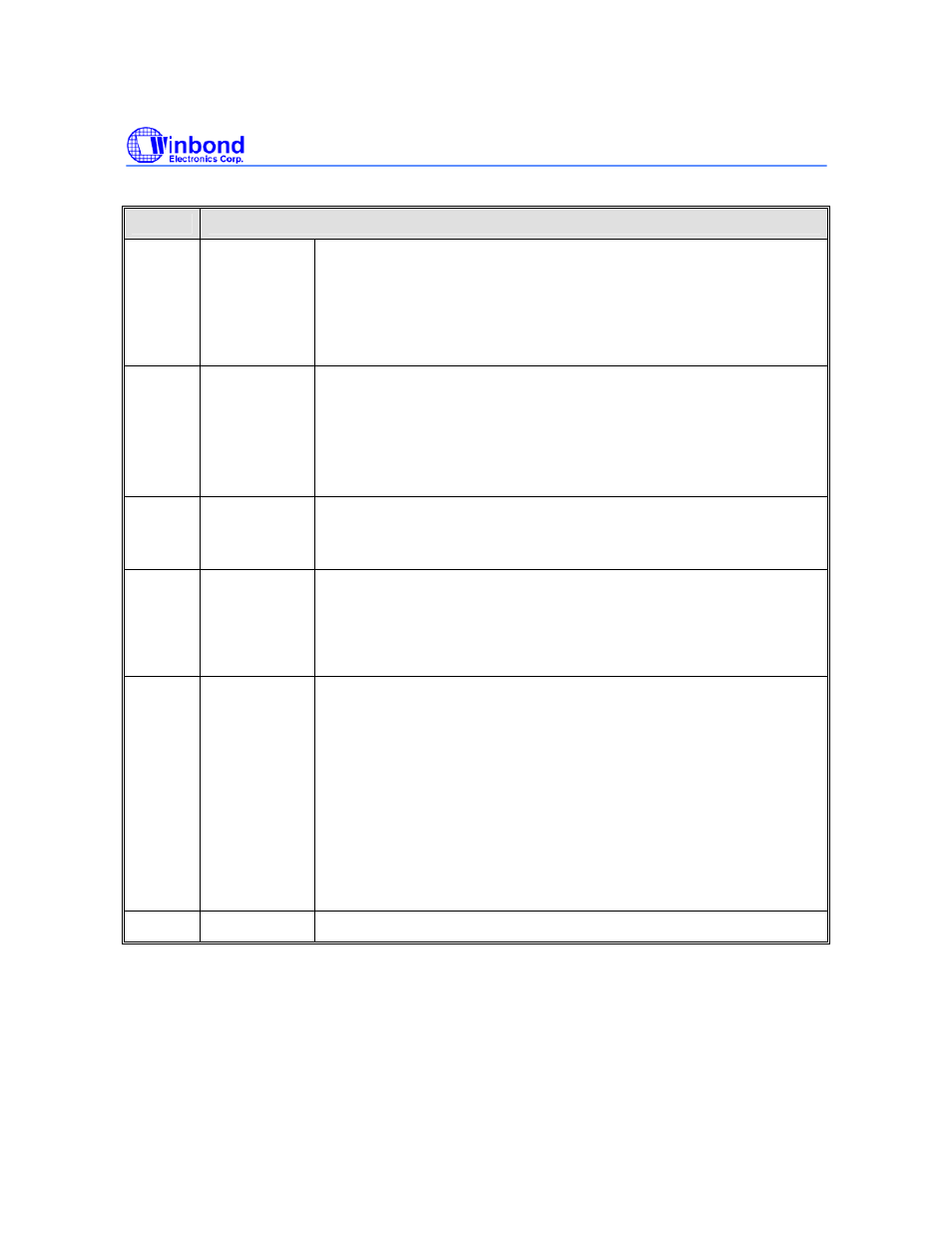

BITS

DESCRIPTIONS

[19] AUTOIEN

Auto initialization Enable

1’b0 = Disables auto initialization

1’b1 = Enables auto initialization, the GDMA_CSRC0/1,

GDMA_CDST0/1,and GDMA_CTCNT0/1 registers are updated by the

GDMA_SRC0/1,GDMA_DST0/1,and GDMA_TCNT0/1 registers

automatically when transfer is complete.

[18] TC

Terminal Count

1’b0 = Channel does not expire

1’b1 = Channel expires; this bit is set only by GDMA hardware, and clear

by software to write logic 0.

TC [18] is the GDMA interrupt flag. TC [18] or GDMATERR[20] will

generate interrupt

[17] BLOCK

Bus Lock

1’b0 = Unlocks the bus during the period of transfer

1’b1 = Locks the bus during the period of transfer

[16] SOFTREQ

Software Triggered GDMA Request

Software can request the GDMA transfer service by setting this bit to 1.

This bit is automatically cleared by hardware when the transfer is

completed. This bit is available only while GDMAMS [3:2] register bits are

set on software mode (memory to memory).

[15]

DM

Demand Mode

1’b0 = Normal external GDMA mode

1’b1 = When this bit is set to 1, the external GDMA operation is speeded

up. When external GDMA device is operating in the demand mode, the

GDMA transfers data as long as the external GDMA request signal

nXDREQ is active. The amount of data transferred depends on how long

the nXDREQ is active. When the nXDREQ is active and GDMA gets the

bus in Demand mode, DMA holds the system bus until the nXDREQ

signal becomes non-active. Therefore, the period of the active nXDREQ

signal should be carefully tuned such that the entire operation does not

exceed an acceptable interval (for example, in a DRAM refresh

operation).

[14] Reserved

-