Rainbow Electronics W90N745CDG User Manual

Page 122

W90N745CD/W90N745CDG

Publication Release Date: September 22, 2006

-

117

-

Revision

A2

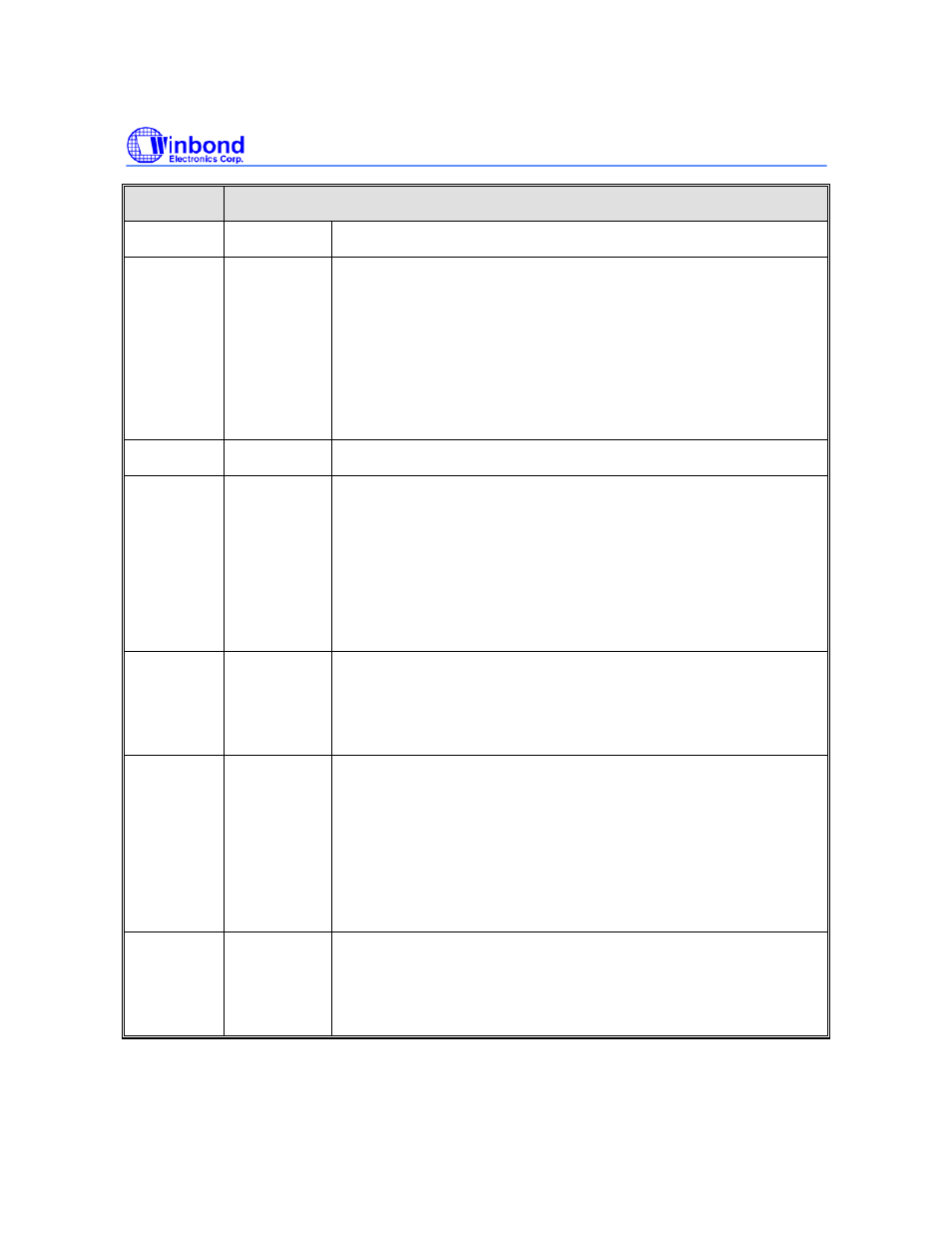

BITS

DESCRIPTIONS

[31:25] Reserved

-

[24] SWR

The SWR (Software Reset) implements a reset function to make the

EMC return default state. The SWR is a self-clear bit. This means

after the software reset finished, the SWR will be cleared

automatically. Enable SWR can also reset all control and status

registers, except for OPMOD bit of MCMDR register.

The EMC re-initial is needed after the software reset completed.

1’b0: Software reset completed.

1’b1: Enable software reset.

[23:22] Reserved

-

[21] LBK

The LBK (Internal Loop Back Select) enables the EMC operating

on internal loop-back mode. If the LBK is enabled, the packet

transmitted out will be loop-backed to Rx. If the EMC is operating on

internal loop-back mode, it also means the EMC is operating on full-

duplex mode and the value of FDUP of MCMDR register is ignored.

Beside, the LBK doesn’t be affected by SWR bit.

1’b0: The EMC operates in normal mode.

1’b1: The EMC operates in internal loop-back mode.

[20] OPMOD

The Operation Mode Select defines the EMC is operating on 10M or

100M bps mode. The OPMOD doesn’t be affected by SWR bit.

1’b0: The EMC operates on 10Mbps mode.

1’b1: The EMC operates on 100Mbps mode.

[19] EnMDC

The Enable MDC Clock Generation controls the MDC clock

generation for MII Management Interface. If the EnMDC is set to 1,

the MDC clock generation is enabled. Otherwise, the MDC clock

generation is disabled. Consequently, if S/W wants to access the

registers of external PHY through MII Management Interface, the

EnMDC must be set to high.

1’b0: Disable MDC clock generation.

1’b1: Enable MDC clock generation.

[18] FDUP

The Full Duplex Mode Select controls that EMC is operating on full

or half duplex mode.

1’b0: The EMC operates on half duplex mode.

1’b1: The EMC operates on full duplex mode.