Pin description – Rainbow Electronics W90N745CDG User Manual

Page 18

W90N745CD/W90N745CDG

Publication Release Date: September 22, 2006

-

13

-

Revision

A2

5. PIN

DESCRIPTION

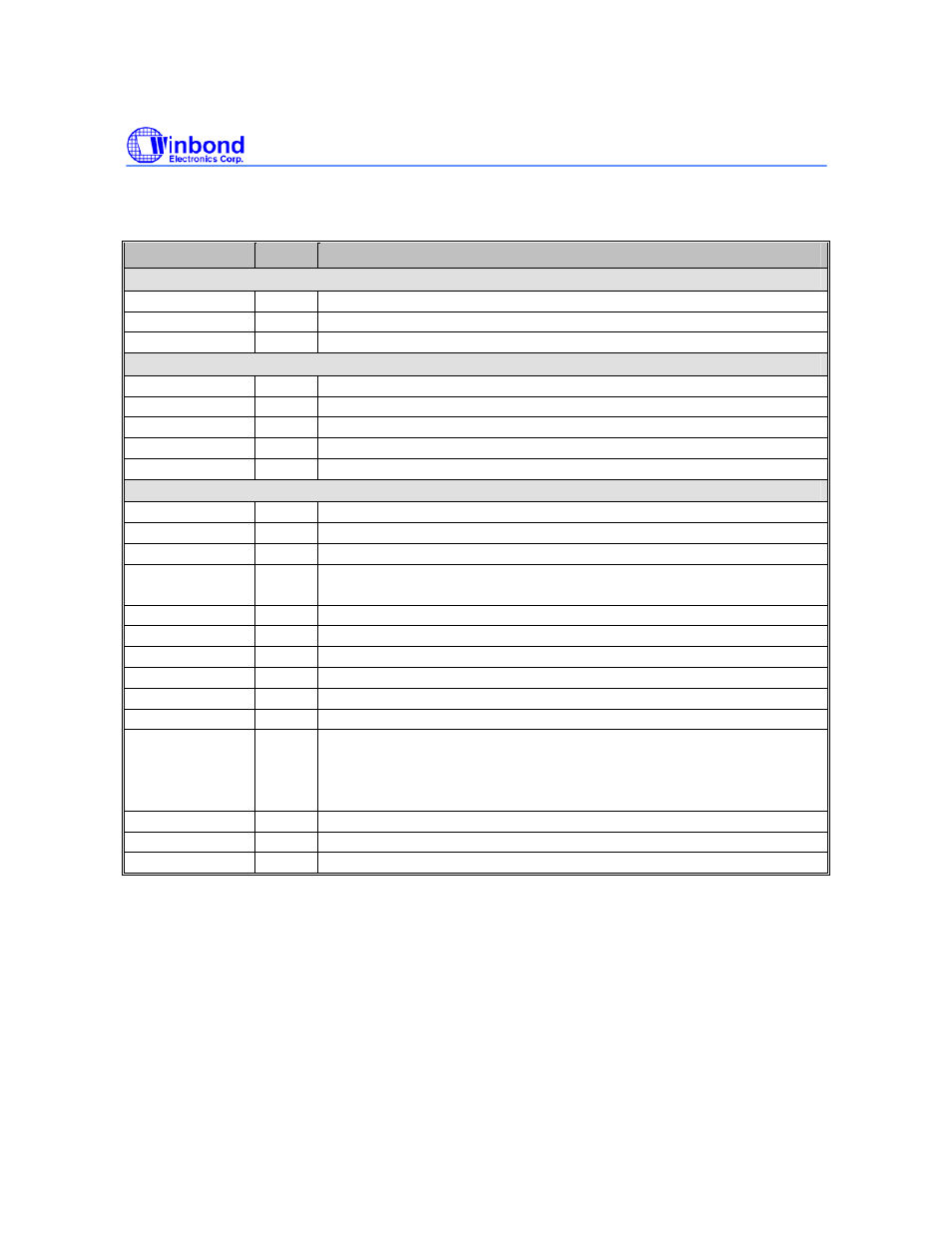

Table 5.1 W90N745 Pins Description

PIN NAME

IO TYPE

DESCRIPTION

Clock & Reset

EXTAL (15M)

I

15MHz External Clock / Crystal Input

XTAL (15M)

O

15MHz Crystal Output

nRESET

IS

System Reset, active-low

JTAG Interface

TMS

IUS

JTAG Test Mode Select, internal pull-up with 70K ohm

TDI

IUS

JTAG Test Data in, internal pull-up with 70K ohm

TDO

O

JTAG Test Data out

TCK

IDS

JTAG Test Clock, internal pull-down with 58K ohm

nTRST

IUS

JTAG Reset, active-low, internal pull-up with 70K ohm

External Bus Interface

A [20:18]

O

Address Bus (MSB) of external memory and IO devices.

A [17:0]

IOS

Address Bus of external memory and IO devices.

D [15:0]

IOS

Data Bus (LSB) of external memory and IO device.

nWBE [1:0] /

SDQM [1:0]

IOS

Write Byte Enable for specific device (nECS [1:0]).

Data Bus Mask signal for SDRAM (nSCS [1:0]), active-low.

nSCS [1:0]

O

SDRAM chip select for two external banks, active-low.

nSRAS

O

Row Address Strobe for SDRAM, active-low.

nSCAS

O

Column Address Strobe for SDRAM, active-low.

MCKE

O

SDRAM Clock Enable, active-high

nSWE

O

SDRAM Write Enable, active-low

MCLK

O

System Master Clock Out, SDRAM clock, output with slew-rate control

nWAIT /

GPIO[30] /

nIRQ3

IUS

External Wait, active-low. This pin indicates that the external devices need

more active cycle during access operation.

General Programmable In/Out Port GPIO[30]. If memory and IO devices in EBI

do not need wait request, it can be configured as GPIO[30] or nIRQ3.

nBTCS

O

ROM/Flash Chip Select, active-low.

nECS [3:0]

IO

External I/O Chip Select, active-low.

nOE

O

ROM/Flash, External Memory Output Enable, active-low.