Rainbow Electronics W90N745CDG User Manual

Page 197

W90N745CD/W90N745CDG

- 192 -

6.8 USB Device Controller

The USB controller interfaces the AHB bus and the USB bus. The USB controller contains both the

AHB master interface and AHB slave interface. CPU programs the USB controller through the AHB

slave interface. For IN or OUT transfer, the USB controller needs to write data to memory or read data

from memory through the AHB master interface. The USB controller also contains the USB

transceiver to interface the USB.

6.8.1 USB

Endpoints

It consists of four endpoints, designated EP0, EPA, EPB and EPC. Each is intended for a particular

use as described below:

EP0: the default endpoint uses control transfer (In/Out) to handle configuration and control functions

required by the USB specification. Maximum packed size is 16 bytes.

EPA: designed as a general endpoint. This endpoint could be programmed to be an Interrupt IN

endpoint or an Isochronous IN endpoint or a Bulk In endpoint or Bulk OUT endpoint.

EPB: designed as a general endpoint. This endpoint could be programmed to be an Interrupt IN

endpoint or an Isochronous IN endpoint or a Bulk In endpoint or Bulk OUT endpoint.

EPC: designed as a general endpoint. This endpoint could be programmed to be an Interrupt IN

endpoint or an Isochronous IN endpoint or a Bulk In endpoint or Bulk OUT endpoint.

6.8.2 Standard Device Request

The USB controller has built-in hard-wired state machine to automatically respond to USB standard

device request. It also supports to detect the class and vendor requests. For Get Descriptor request

and Class or Vendor command, the firmware will control these procedures.

6.8.3 USB Device Register Description

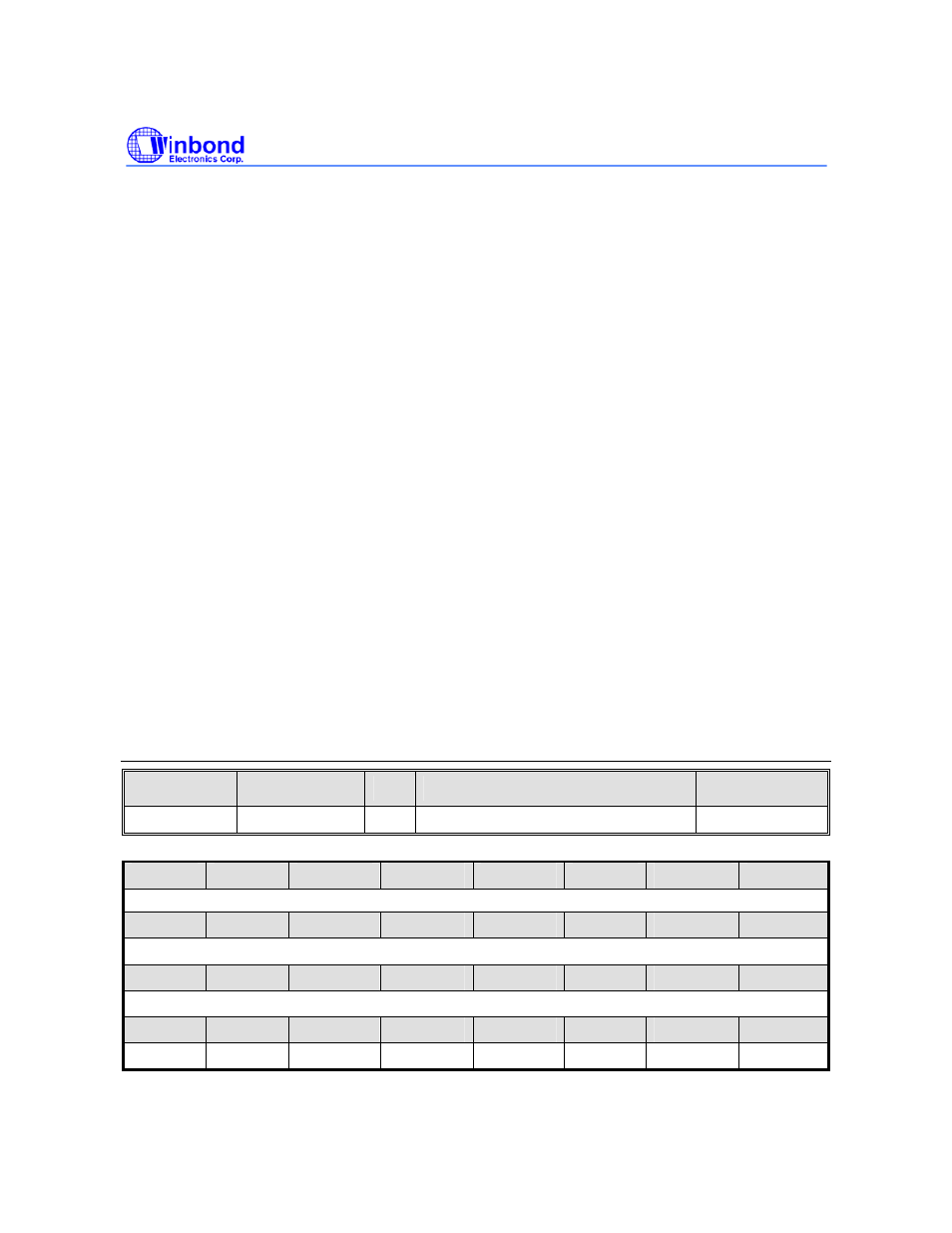

USB Control Register (USB_CTL)

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET VALUE

USB_CTL

0xFFF0_6000

R/W

USB control register

0x0000_0000

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved

7

6

5

4

3

2

1

0

CCMD VCMD SIE_RCV

SUS_TST

RWU_EN

SUSP USB_RST USB_EN