Rainbow Electronics W90N745CDG User Manual

Page 121

W90N745CD/W90N745CDG

- 116 -

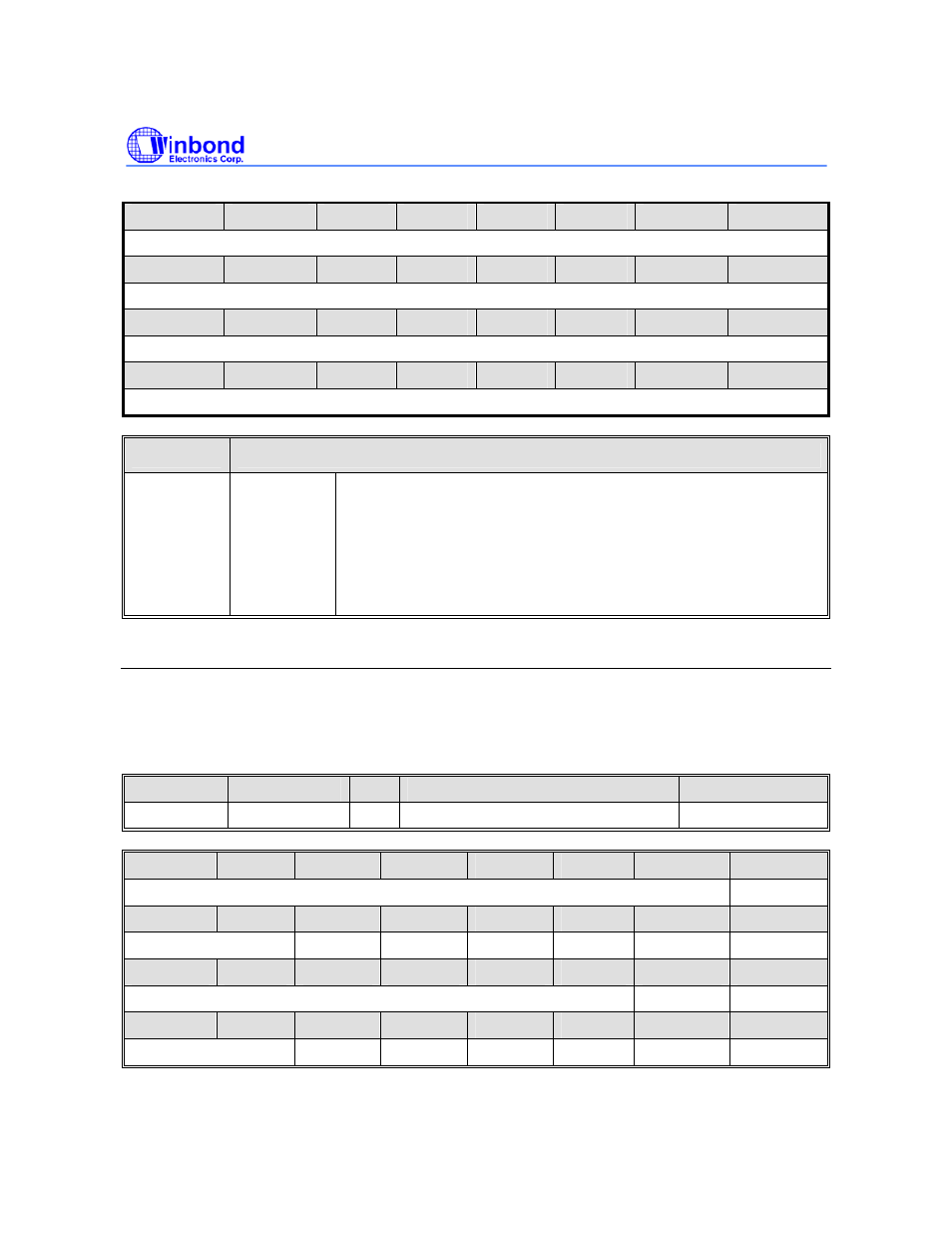

31

30

29

28

27

26

25

24

RXDLSA

23

22

21

20

19

18

17

16

RXDLSA

15

14

13

12

11

10

9

8

RXDLSA

7

6

5

4

3

2

1

0

RXDLSA

BITS

DESCRIPTIONS

[31:0] RXDLSA

The RXDLSA(Receive Descriptor Link-List Start Address) keeps

the start address of receive descriptor link-list. If the S/W enables the

bit RXON of MCMDR register, the content of RXDLSA will be loaded

into the current receive descriptor start address register (CRXDSA).

The RXDLSA doesn’t be updated by EMC. During the operation,

EMC will ignore the bits [1:0] of RXDLSA. This means that each Rx

descriptor always must locate at word boundary memory address.

MAC Command Register (MCMDR)

The MCMDR provides the control information for EMC. Some command settings affect both frame

transmission and reception, such as bit FDUP, the full/half duplex mode selection, or bit OPMOD, the

100/10M bps mode selection. Some command settings control frame transmission and reception

separately, likes bit TXON and RXON.

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET VALUE

MCMDR

0xFFF0_3090

R/W

MAC Command Register

0x0000_0000

31

30

29

28

27

26

25

24

Reserved SWR

23

22

21

20

19

18

17

16

Reserved

LBK OPMOD

EnMDC FDUP EnSQE SDPZ

15

14

13

12

11

10

9

8

Reserved NDEF

TXON

7

6

5

4

3

2

1

0

Reserved SPCRC

AEP

ACP

ARP

ALP RXON