Rainbow Electronics W90N745CDG User Manual

Page 349

W90N745CD/W90N745CDG

Publication Release Date: September 22, 2006

-

345

-

Revision

A2

I

2

C Command Register 0/1 (I

2

C_CMDR 0/1)

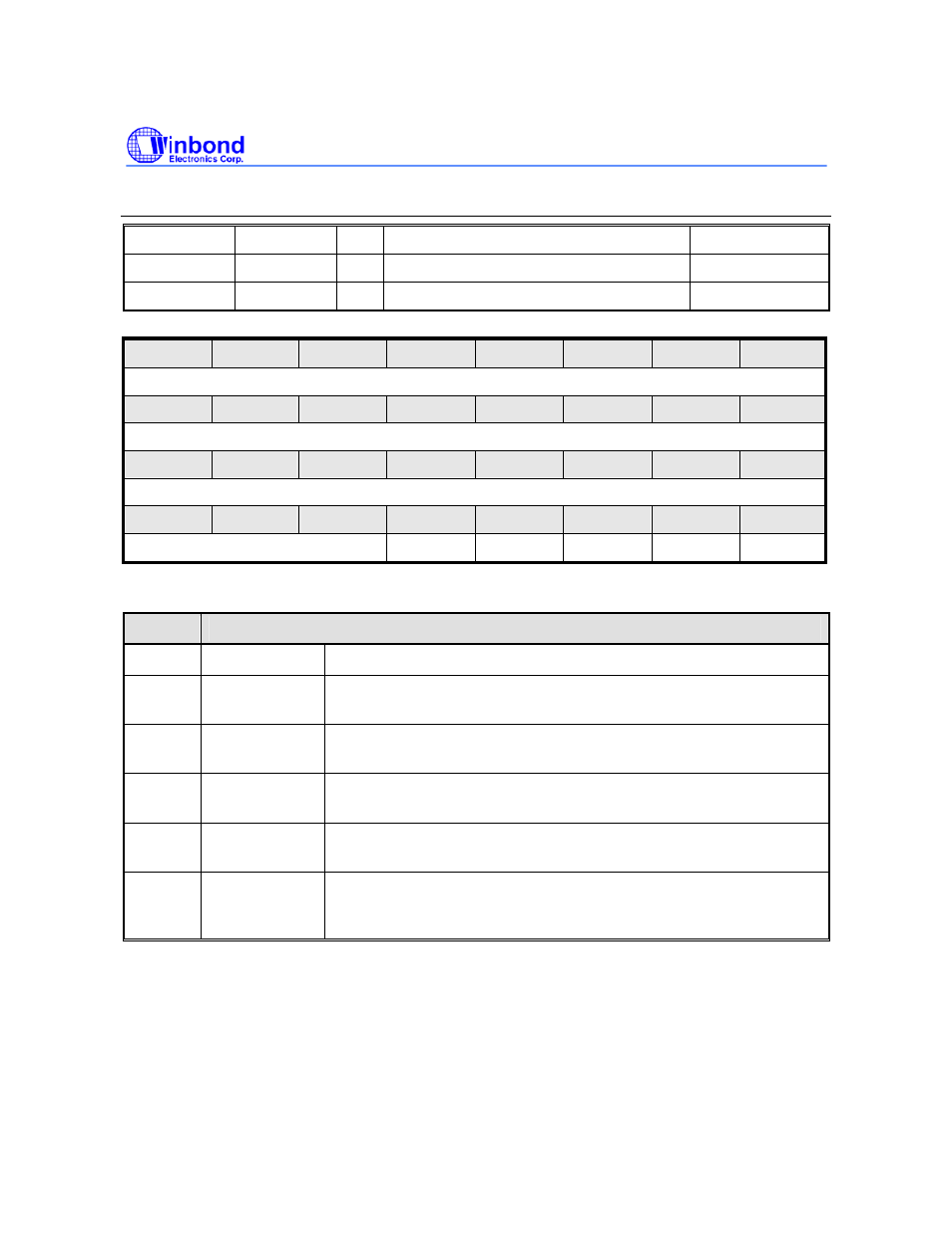

REGISTER ADDRESS

R/W

DESCRIPTION

RESET

VALUE

I

2

C_CMDR0

0xFFF8_6008

R/W

I

2

C Command Register 0

0x0000_0000

I

2

C_CMDR1

0xFFF8_6108

R/W

I

2

C Command Register 1

0x0000_0000

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved

7

6

5

4

3

2

1

0

Reserved

START

STOP

READ

WRITE

ACK

NOTE:

Software can write this register only when I

2

C_EN = 1.

BITS

DESCRIPTIONS

[31:5]

Reserved

Reserved

[4]

START

Generate Start Condition

Generate (repeated) start condition on I

2

C bus.

[3]

STOP

Generate Stop Condition

Generate stop condition on I

2

C bus.

[2]

READ

Read Data From Slave

Retrieve data from slave.

[1]

WRITE

Write Data To Slave

Transmit data to slave.

[0]

ACK

Send Acknowledge To Slave

When I

2

C behaves as a receiver, sent ACK (ACK = ‘0’) or NACK (ACK

= ‘1’) to slave.

NOTE:

The START, STOP, READ and WRITE bits are cleared automatically while transfer finished. READ and WRITE cannot

be set concurrently.