Rainbow Electronics W90N745CDG User Manual

Page 241

W90N745CD/W90N745CDG

- 236 -

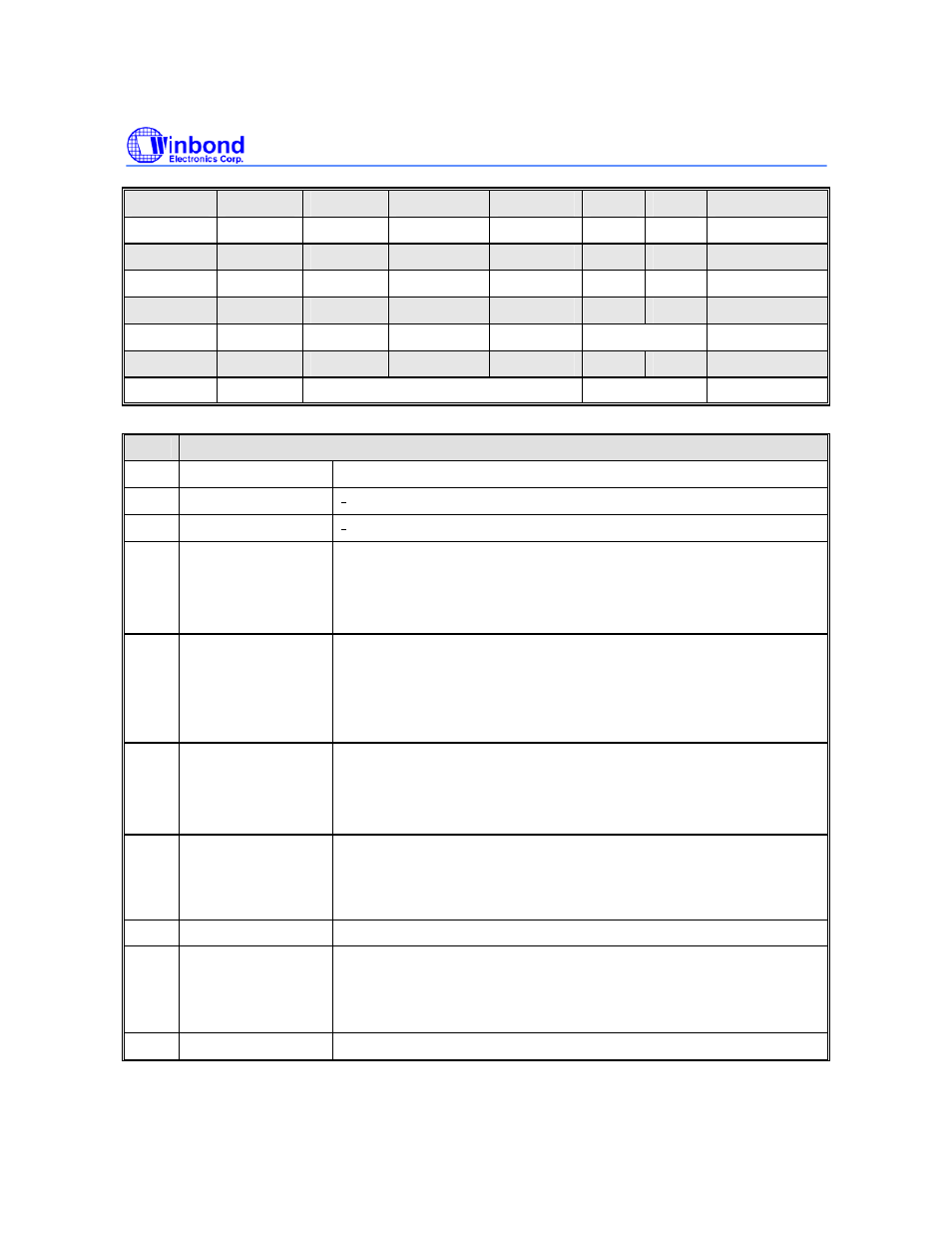

BITS

DESCRIPTIONS

[15]

Reserved

-

[14]

Reserved

-

[13]

Reserved

-

[12] R_DMA_IRQ

When recording, when the DMA destination current address reach the DMA

destination end address or middle address, the R_DMA_IRQ bit will be set to

1 automatically, and this bit could be cleared to 0 by CPU. The bit is

hardwired to ARM as interrupt request signal with an inverter.

The R_DMA_IRQ bit is read/write (

write 1 to clear

)

[11] T_DMA_IRQ

Transmit DMA interrupt request bit. When DMA current address reach the

middle address (((ACTL_DESE – ACTL_DESB)-1)/2 + ACTL_DESB) or

reach the end address ACTL_DESB, the bit T_DMA_IRQ will be set to 1, and

this bit could be clear to 0 by write “1” by CPU. And the bit is hardwired to

ARM as interrupt request signal with an inverter.

The T_DMA_IRQ bit is read/write (

write 1 to clear

).

[8] I²S_AC_PIN_SEL

I

²

S or AC-link pin selection

• If I

²

S_AC_PIN_SEL = 0, the pins select I

²

S

• If I

²

S_AC_PIN_SEL = 1, the pins select AC-link

The I

²

S_AC_PIN_SEL bis is read/write

[7] FIFO_TH

FIFO threshold control bit

• If FIFO_TH=0, the FIFO threshold is 8 level

• If FIFO_TH=1, the FIFO threshold is 4 level

The FIFO_TH bit is read/write

[6]

Reserved

[2:1]

BLOCK_EN[1:0]

Audio interface type selection

• If BLOCK_EN[0]=0/1, I

²

S interface is disable/enable

• If BLOCK_EN[1]=0/1, AC-link interface is disable/enable

The BLOCK_EN[1:0] bits are read/write

[0]

Reserved

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

Reserved Reserved Reserved R_DMA_IRQ

T_DMA_IRQ

Reserved I

²

S_AC_PIN_SEL

7

6

5

4

3

2

1

0

FIFO_TH Reserved

Reserved BLOCK_EN[1:0]

Reserved