Rainbow Electronics W90N745CDG User Manual

Page 187

W90N745CD/W90N745CDG

- 182 -

BITS

DESCRIPTION

31 FINTVT

FrameIntervalToggle

This bit is toggled by HCD when it loads a new value into Frame Interval.

[30:16]

FSLDP

FSLargestDataPacket

This field specifies a value that is loaded into the Largest Data Packet

Counter at the beginning of each frame.

[15:14] Reserved Reserved. Read/Write 0's

[13:0] FINTV

Frame Interval

This field specifies the length of a frame as (bit times - 1). For 12,000 bit

times in a frame, a value of 11,999 is stored here.

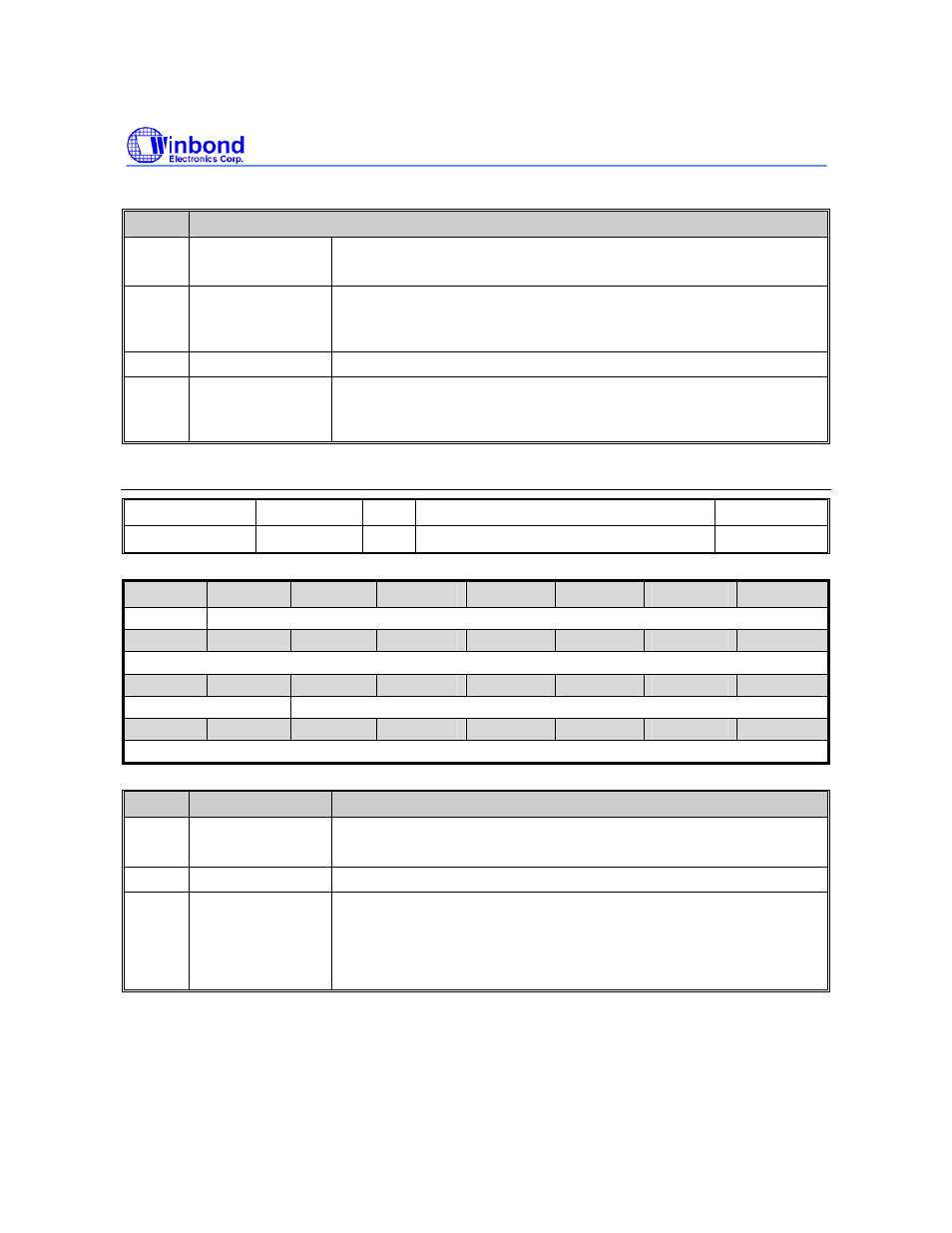

Host Controller Frame Remaining Register

REGISTER ADDRESS

R/W

DESCRIPTION

RESET

VALUE

HcFmInterval 0xFFF0_5038

R

Host Controller Frame Remaining Register 0x0000_0000

31

30

29

28

27

26

25

24

FRMT

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved

FRM

7

6

5

4

3

2

1

0

FRM

BITS

DESCRIPTION

[31] FRMT

FrameRemainingToggle

Loaded with FrameIntervalToggle when Frame Remaining is loaded.

[30:14] Reserved Reserved. Read/Write 0's

[13:0] FRM

Frame Remaining

When the Host Controller is in the U

SB

O

PERATIONAL

state, this 14-bit field

decrements each 12 MHz clock period. When the count reaches 0, (end of

frame) the counter reloads with Frame Interval. In addition, the counter

loads when the Host Controller transitions into U

SB

O

PERATIONAL

.