Rainbow Electronics W90N745CDG User Manual

Page 412

W90N745CD/W90N745CDG

- 408 -

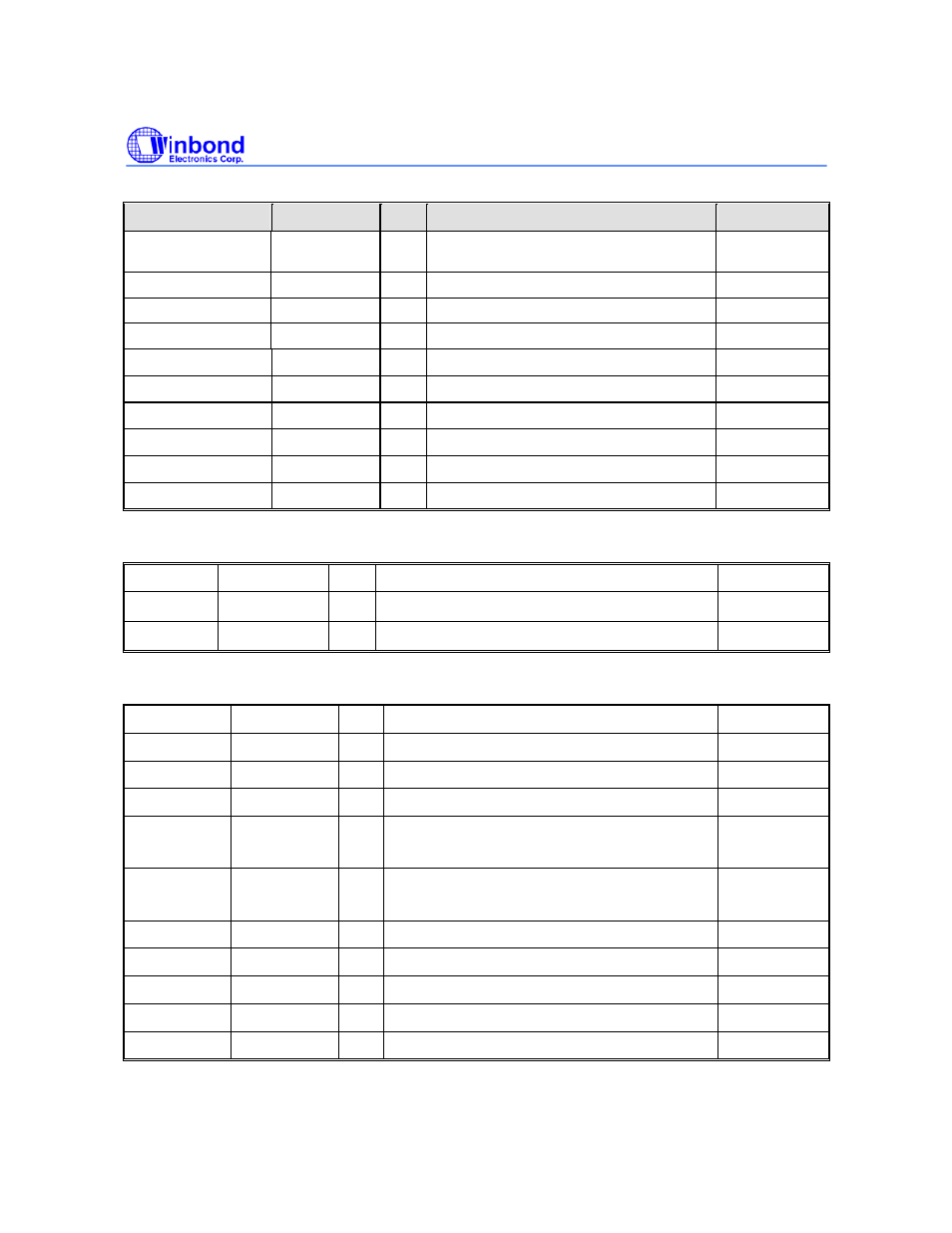

Audio Control Register Map, continued

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET VALUE

ACTL_PDSTC 0xFFF0_9020

R

DMA destination current address

register for play

0x0000_0000

ACTL_PSR

0xFFF0_9024 R/W

Play status register

0x0000_0004

ACTL_I²SCON 0xFFF0_9028

R/W

I²S control register

0x0000_0000

ACTL_ACCON 0xFFF0_902C

R/W

AC-link control register

0x0000_0000

ACTL_ACOS0

0xFFF0_9030 R/W AC-link out slot 0

0x0000_0000

ACTL_ACOS1

0xFFF0_9034 R/W AC-link out slot 1

0x0000_0080

ACTL_ACOS2

0xFFF0_9038 R/W AC-link out slot 2

0x0000_0000

ACTL_ACIS0

0xFFF0_903C

R AC-link in slot 0

0x0000_0000

ACTL_ACIS1

0xFFF0_9040

R AC-link in slot 1

0x0000_0000

ACTL_ACIS2

0xFFF0_9044

R AC-link in slot 2

0x0000_0000

Cache Controller Test Registers Map

REGISTER ADDRESS R/W

DESCRIPTION

RESET

VALUE

CTEST0

0xFFF6_0000 R/W

Cache test register 0

0x0000_0000

CTEST1

0xFFF6_0004

R

Cache test register 1

0x0000_0000

UART0 Control Registers Map

REGISTER ADDRESS R/W

DESCRIPTION

RESET

VALUE

UART0_RBR 0xFFF8_0000

R

Receive Buffer Register (DLAB = 0)

Undefined

UART0_THR 0xFFF8_0000 W

Transmit Holding Register (DLAB = 0)

Undefined

UART0_IER 0xFFF8_0004 R/W

Interrupt

Enable Register (DLAB = 0)

0x0000_0000

UART0_DLL 0xFFF8_0000 R/W

Divisor Latch Register (LS)

(DLAB = 1)

0x0000_0000

UART0_DLM 0xFFF8_0004 R/W

Divisor Latch Register (MS)

(DLAB = 1)

0x0000_0000

UART0_IIR 0xFFF8_0008 R

Interrupt

Identification Register

0x8181_8181

UART0_FCR 0xFFF8_0008 W

FIFO Control Register

Undefined

UART0_LCR 0xFFF8_000C R/W Line Control Register

0x0000_0000

UART0_LSR 0xFFF8_0014 R

Line Status Register

0x6060_6060

UART0_TOR 0xFFF8_001C

R

Time Out Register

0x0000_0000