Rainbow Electronics W90N745CDG User Manual

Page 352

W90N745CD/W90N745CDG

- 348 -

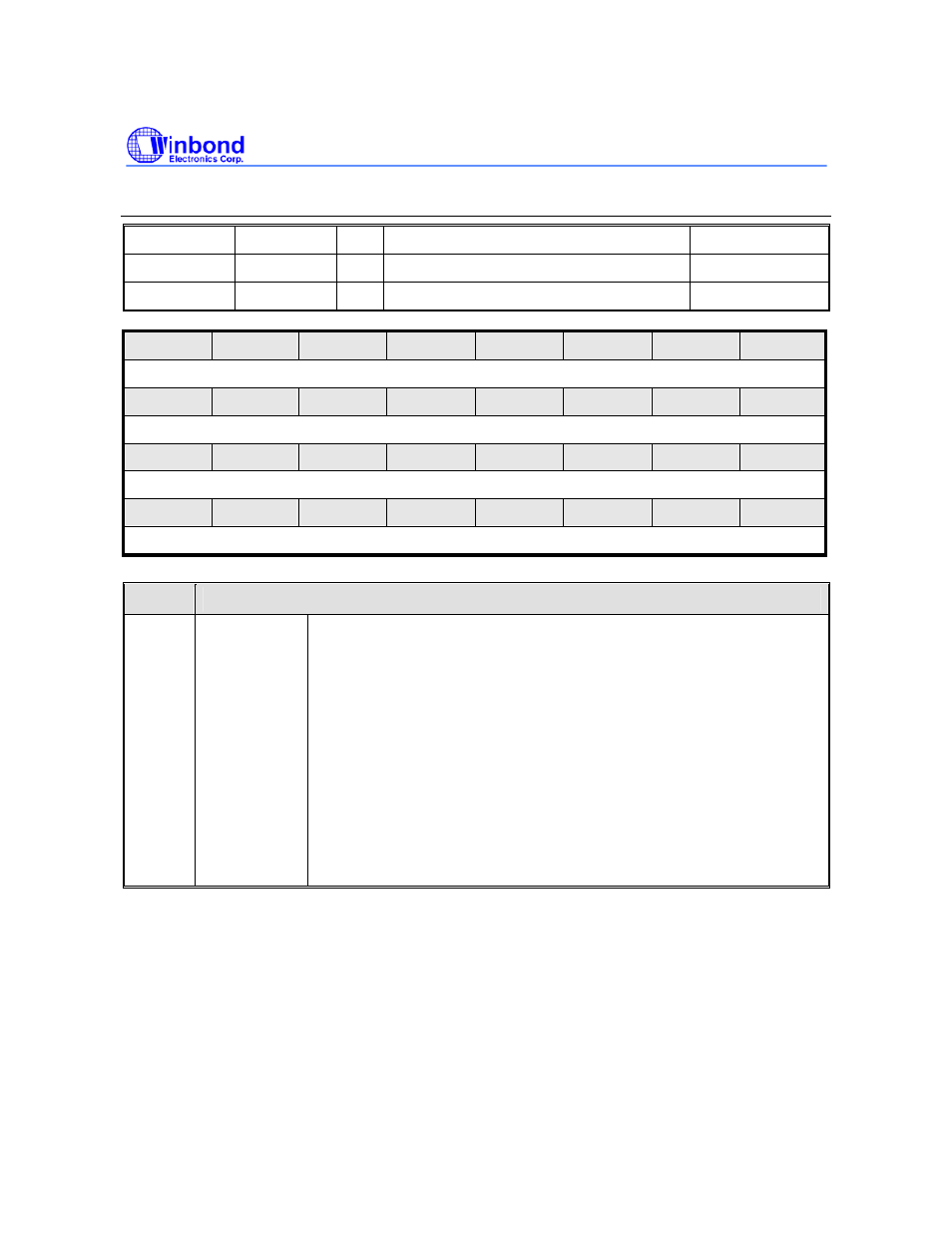

I

2

C Data Transmit Register 0/1 (I

2

C_TxR 0/1)

REGISTER ADDRESS

R/W

DESCRIPTION

RESET

VALUE

I

2

C_TXR0

0xFFF8_6014

R/W

I

2

C Data Transmit Register

0x0000_0000

I

2

C_TXR1

0xFFF8_6114

R/W

I

2

C Data Transmit Register

0x0000_0000

31

30

29

28

27

26

25

24

Tx

[31:24]

23

22

21

20

19

18

17

16

Tx

[23:16]

15

14

13

12

11

10

9

8

Tx

[15:8]

7

6

5

4

3

2

1

0

Tx

[7:0]

BITS

DESCRIPTIONS

[31:0]

Tx

Data Transmit Register

The I

2

C core used 32-bit transmit buffer and provide multi-byte

transmit function. Set CSR[Tx_NUM] to a value that you want to

transmit. I

2

C core will always issue a transfer from the highest byte

first. For example, if CSR[Tx_NUM] = 0x3, Tx[31:24] will be

transmitted first, then Tx[23:16], and so on.

In case of a data transfer, all bits will be treated as data.

In case of a slave address transfer, the first 7 bits will be treated as 7-

bit address and the LSB represent the R/W bit. In this case,

LSB = 1, reading from slave

LSB = 0, writing to slave