Rainbow Electronics W90N745CDG User Manual

Page 286

W90N745CD/W90N745CDG

Publication Release Date: September 22, 2006

-

281

-

Revision

A2

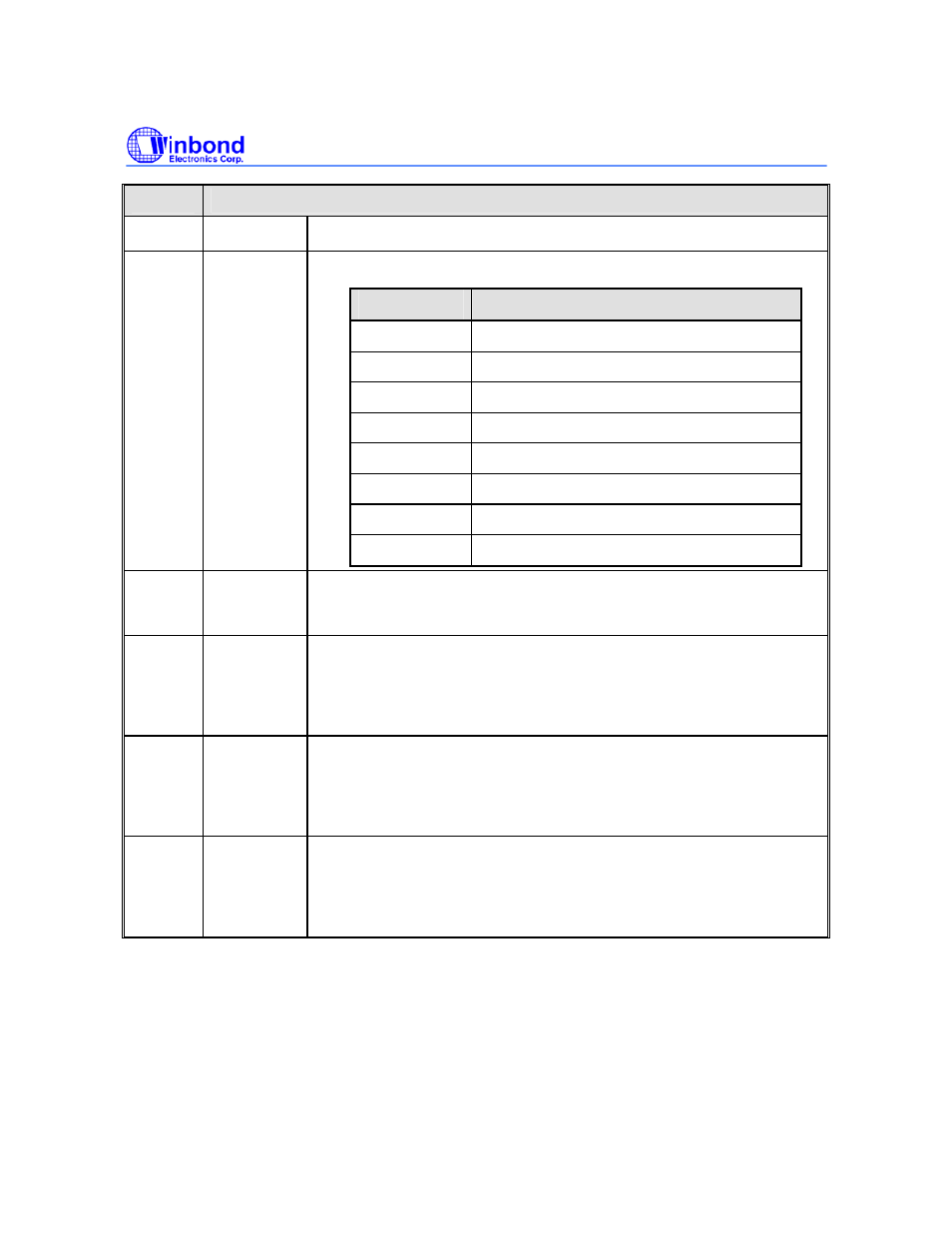

BITS

DESCRIPTIONS

[31:8]

Reserved -

[7:4]

RFITL

RX FIFO Interrupt (Irpt_RDA) Trigger Level

RFITL

Irpt_RDA Trigger Level (Bytes)

0000

01

0001

04

0010

08

0011

14

0100

30

0101

46

0110

62

others

62

[3]

DMS

DMA Mode Select

The DMA function is not implemented in this version.

[2]

TFR

TX FIFO Reset

Setting this bit will generate an OSC cycle reset pulse to reset TX FIFO.

The TX FIFO becomes empty (TX pointer is reset to 0) after such reset.

This bit is returned to 0 automatically after the reset pulse is generated.

[1]

RFR

RX FIFO Reset

Setting this bit will generate an OSC cycle reset pulse to reset RX FIFO.

The RX FIFO becomes empty (RX pointer is reset to 0) after such reset.

This bit is returned to 0 automatically after the reset pulse is generated.

[0]

FME

FIFO Mode Enable

Because UART is always operating in the FIFO mode, writing this bit has

no effect while reading always gets logical one. This bit must be 1 when

other FCR bits are written to; otherwise, they will not be programmed.