Rainbow Electronics W90N745CDG User Manual

Page 143

W90N745CD/W90N745CDG

- 138 -

Continued.

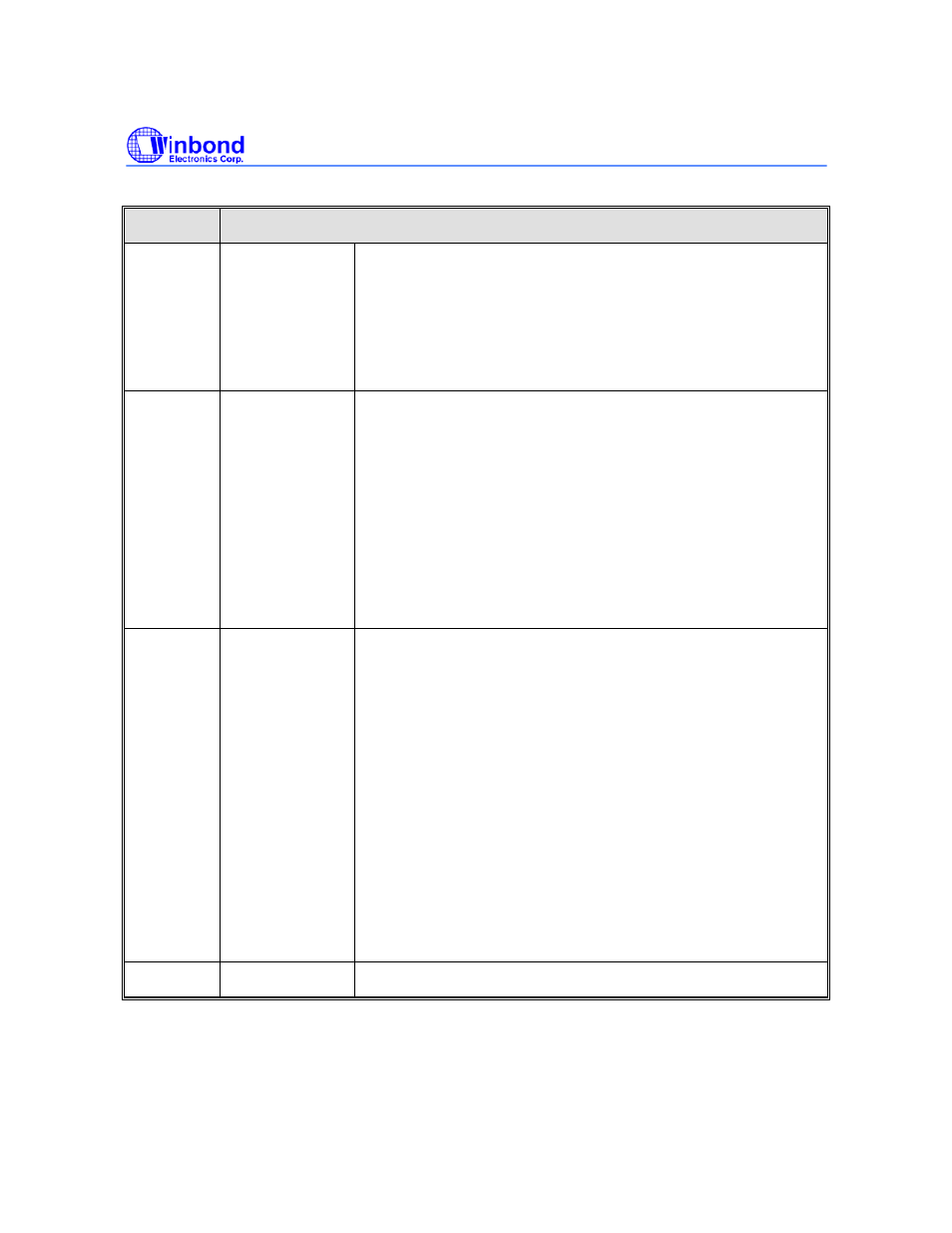

BITS

DESCRIPTIONS

[18] TXCP

The Transmit Completion Interrupt indicates the packet

transmission has completed correctly.

If the TXCP is high and EnTXCP of MIEN register is enabled, the

TxINTR will be high. Write 1 to this bit clears the TXCP status.

1’b0: The packet transmission doesn’t complete.

1’b1: The packet transmission has completed.

[17] TXEMP

The Transmit FIFO Underflow Interrupt high indicates the

TxFIFO underflow occurred during packet transmission. While the

TxFIFO underflow occurred, the EMC will retransmit the packet

automatically without S/W intervention. If the TxFIFO underflow

occurred often, it is recommended that modify TxFIFO threshold

control, the TxTHD of FFTCR register, to higher level.

If the TXEMP is high and EnTXEMP of MIEN register is enabled,

the TxINTR will be high. Write 1 to this bit clears the TXEMP

status.

1’b0: No TxFIFO underflow occurred during packet transmission.

1’b0: TxFIFO underflow occurred during packet transmission.

[16] TXINTR

The Transmit Interrupt indicates the Tx interrupt status.

If TXINTR high and its corresponding enable bit, EnTXINTR of

MISTA register, is also high indicates the EMC generates Tx

interrupt to CPU. If TXINTR is high but EnTXINTR of MISTA is

disabled, no Tx interrupt is generated.

The TXINTR is logic OR result of the bits 17~24 in MISTA register

do logic AND with the corresponding bits in MIEN register. In

other words, if one of the bits 17~24 in MISTA register is high and

its corresponding enable bit in MIEN register is also enabled, the

TXINTR will be high. Because the TXINTR is a logic OR result,

clears bits 17~24 of MISTA register makes TXINTR be cleared,

too.

1’b0: No status of bits 17~24 in MISTA is set or no enable of bits

17~24 in MIEN is turned on.

1’b1: At least one status of bits 17~24 in MISTA is set and its

corresponding enable bit is turned on.

[15]

Reserved