Rainbow Electronics W90N745CDG User Manual

Page 164

W90N745CD/W90N745CDG

Publication Release Date: September 22, 2006

-

159

-

Revision

A2

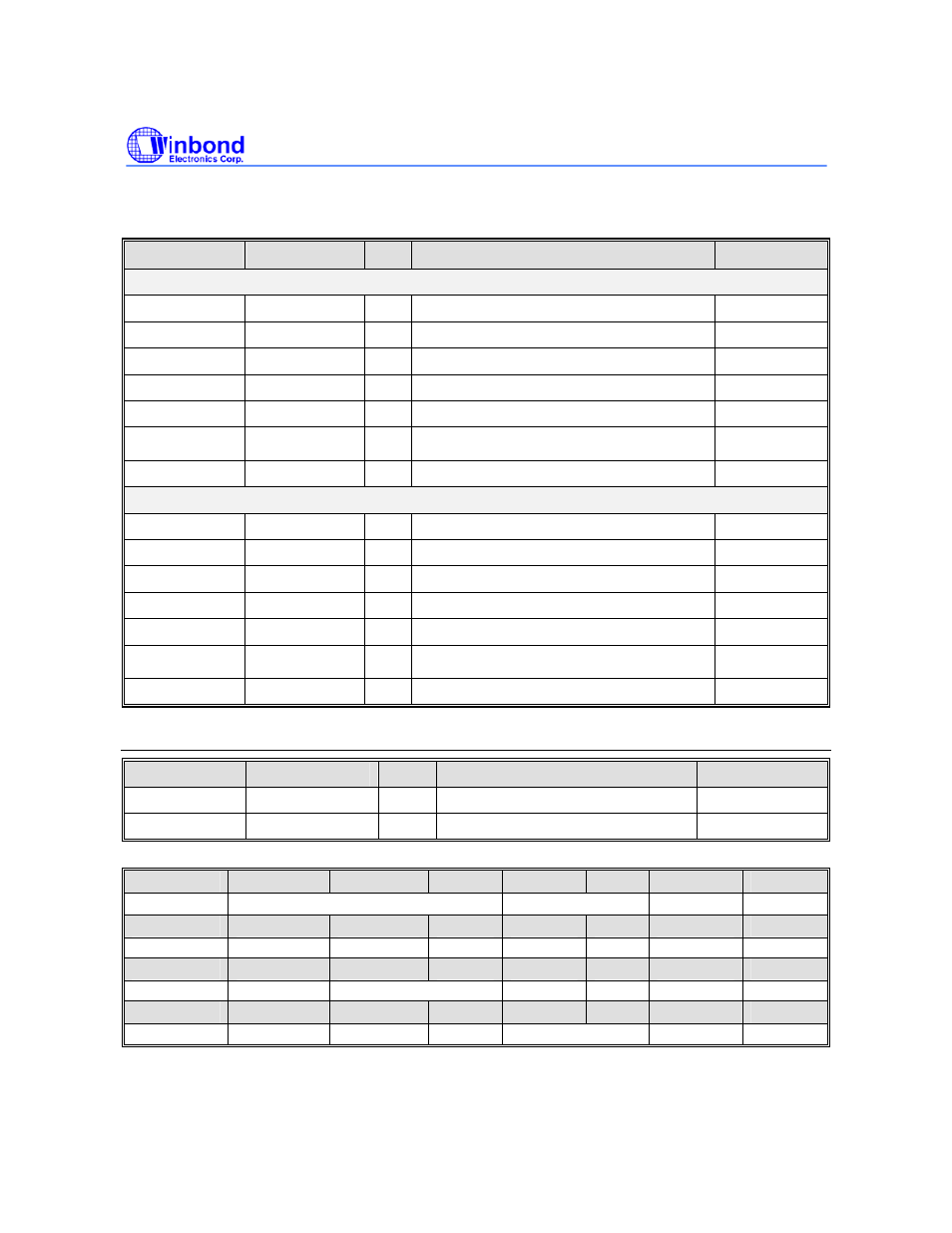

6.6.2 GDMA Register Map

R: read only, W: write only, R/W: both read and write, C: Only value 0 can be written

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET VALUE

Channel 0

GDMA_CTL0 0xFFF0_4000

R/W

Channel 0 Control Register

0x0000_0000

GDMA_SRCB0 0xFFF0_4004 R/W

Channel 0 Source Base Address Register

0x0000_0000

GDMA_DSTB0 0xFFF0_4008 R/W

Channel 0 Destination Base Address Register

0x0000_0000

GDMA_TCNT0 0xFFF0_400C R/W

Channel 0 Transfer Count Register

0x0000_0000

GDMA_CSRC0 0xFFF0_4010 R

Channel 0 Current Source Address Register

0x0000_0000

GDMA_CDST0 0xFFF0_4014 R

Channel 0 Current Destination Address

Register

0x0000_0000

GDMA_CTCNT0 0xFFF0_4018 R

Channel 0 Current Transfer Count Register

0x0000_0000

Channel 1

GDMA_CTL1 0xFFF0_4020

R/W

Channel 1 Control Register

0x0000_0000

GDMA_SRCB1 0xFFF0_4024 R/W

Channel 1 Source Base Address Register

0x0000_0000

GDMA_DSTB1 0xFFF0_4028 R/W

Channel 1 Destination Base Address Register

0x0000_0000

GDMA_TCNT1 0xFFF0_402C R/W

Channel 1 Transfer Count Register

0x0000_0000

GDMA_CSRC1 0xFFF0_4030 R

Channel 1 Current Source Address Register

0x0000_0000

GDMA_CDST1 0xFFF0_4034 R

Channel 1 Current Destination Address

Register

0x0000_0000

GDMA_CTCNT1 0xFFF0_4038 R

Channel 1 Current Transfer Count Register

0x0000_0000

Channel 0/1 Control Register (GDMA_CTL0, GDMA_CTL1)

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET VALUE

GDMA_CTL0 0xFFF0_4000 R/W

Channel 0 Control Register

0x0000_0000

GDMA_CTL1 0xFFF0_4020 R/W

Channel 1 Control Register

0x0000_0000

31

30

29

28

27

26

25

24

RESERVED

TC_WIDTH

REQ_SEL

REQ_ATV ACK_ATV

23

22

21

20

19

18

17

16

RW_TC SABNDERR

DABNDERR GDMAERR AUTOIEN

TC BLOCK

SOFTREQ

15

14

13

12

11

10

9

8

DM

RESERVED

TWS SBMS

RESERVED

BME SIEN

7

6

5

4

3

2

1

0

SAFIX DAFIX SADIR

DADIR GDMAMS

RESERVED

GDMAEN