Rainbow Electronics W90N745CDG User Manual

Page 44

W90N745CD/W90N745CDG

Publication Release Date: September 22, 2006

-

39

-

Revision

A2

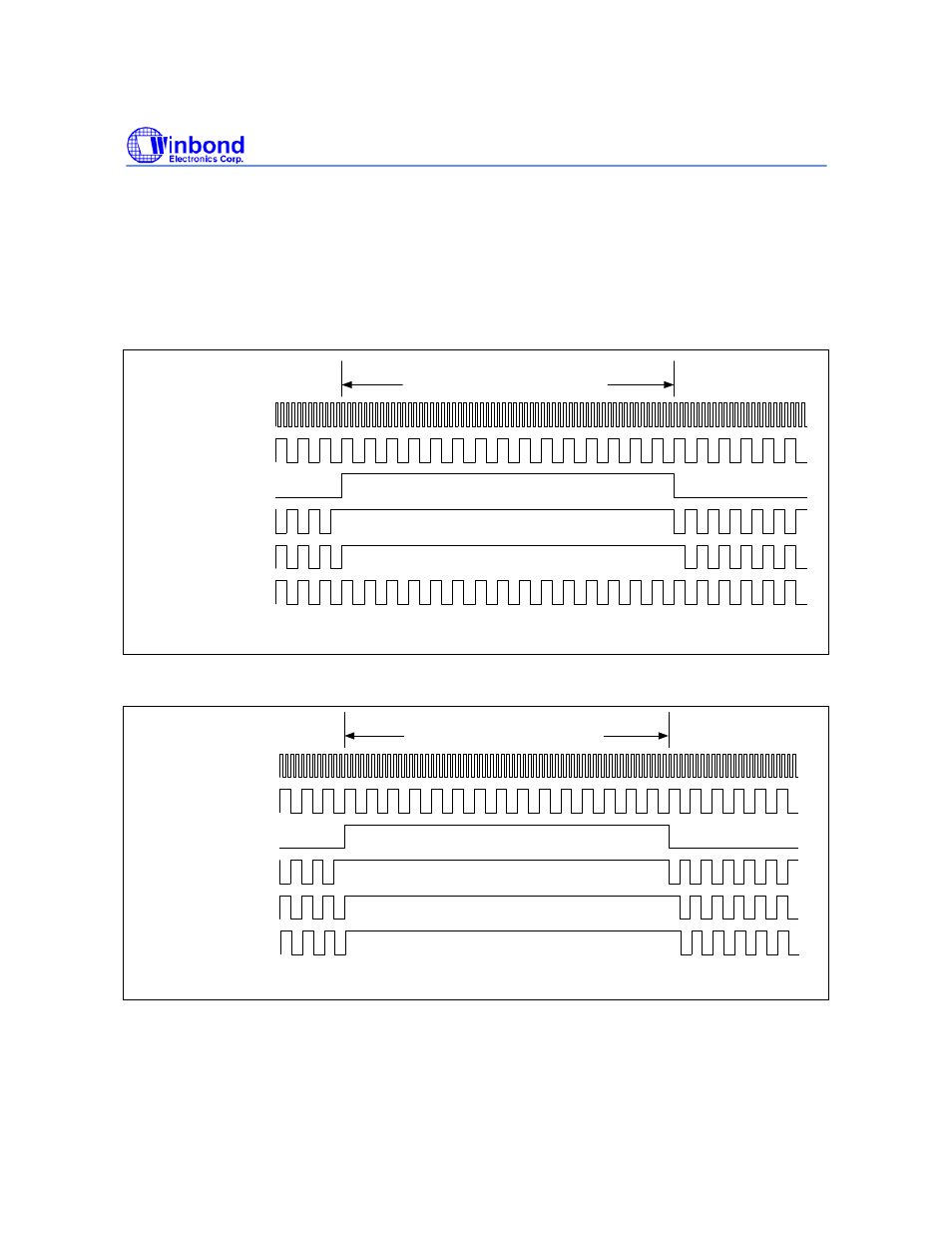

IDLE MODE

If the IDLE bit in Power Management Control Register (PMCON) is set, the ARM CORE clock source

will be halted, the ARM CORE will not go forward. The AHB or APB clocks still active except the clock

to cache controller and ARM are stopped. W90N745 will exit idle state when nIRQ or nFIQ from any

peripheral is revived; like keypad, timer overflow interrupts and so on. The memory controller can also

be forced to enter idle state if both MIDLE and IDLE bits are set. Software must switch SDRAM into

self-refresh mode before forcing memory to enter idle mode.

FOUT

(PLL)

HCLK

idle_state

MCLK

(ARM)

HCLK

(cache)

IDLE Period

HCLK

(memc)

Case1. IDLE=1, PD=0, MIDLE=0

Figure 6.2.7 Clock management for system idle mode

FOUT

(PLL)

HCLK

idle_state

MCLK

(ARM)

HCLK

(cache)

IDLE Period

HCLK

(memc)

Case2. IDLE=1, PD=0, MIDLE=1

Figure 6.2.8 Clock management for system and memory idle mode

- MAX5151 (16 pages)

- MAXQ3108 (64 pages)

- MAX5661 (39 pages)

- MAX6691 (7 pages)

- MAX5362 (12 pages)

- ADC10158 (26 pages)

- MAX8922L (14 pages)

- MAX8596Z (8 pages)

- MAX7491 (18 pages)

- MAX15040 (15 pages)

- MAX5177 (16 pages)

- ADC08138 (22 pages)

- MAX5961 (42 pages)

- T89C51RD2 (86 pages)

- MAX16055 (9 pages)

- MAX6659 (17 pages)

- ADC0820 (20 pages)

- MAX6678 (19 pages)

- MAX8884Z (15 pages)

- MAX16915 (9 pages)

- MAX8620 (18 pages)

- MAX5144 (12 pages)

- MAX6670 (8 pages)

- MAX8760 (39 pages)

- W78C32C (14 pages)

- MX7533 (8 pages)

- MAX8727 (13 pages)

- MAX9053 (15 pages)

- W78C54 (16 pages)

- MAX8614B (15 pages)

- W90N740 (219 pages)

- MAX6626 (13 pages)

- ADC10738 (30 pages)

- MAX17000 (31 pages)

- MAX5051 (21 pages)

- MAXQ1004 (18 pages)

- MAX6871 (51 pages)

- MX7847 (12 pages)

- MAX6608 (6 pages)

- MAX17083 (15 pages)

- MAX6641 (17 pages)

- MAX5251 (16 pages)

- MAX6338 (8 pages)

- MAX6690 (16 pages)

- MAX8668 (18 pages)