Rainbow Electronics W90N745CDG User Manual

Page 171

W90N745CD/W90N745CDG

- 166 -

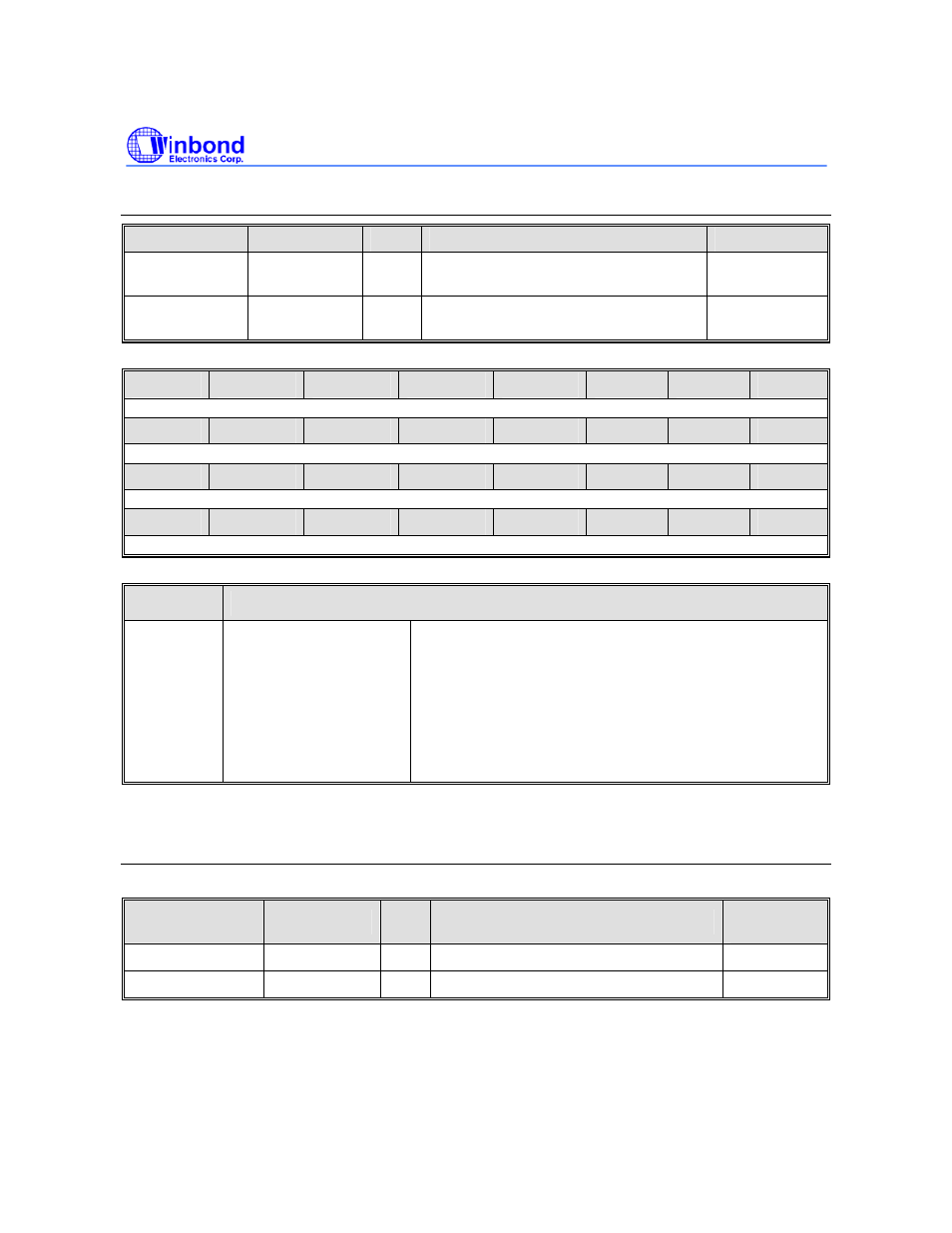

Channel 0/1 Current Destination Register (GDMA_CDST0, GDMA_CDST1)

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET VALUE

GDMA_CDST0 0xFFF0_4014 R

Channel 0 Current Destination Address

Register

0x0000_0000

GDMA_CDST1 0xFFF0_4034 R

Channel 1 Current Destination Address

Register

0x0000_0000

31

30

29

28

27

26

25

24

CURRENT_DST_ADDR [31:24]

23

22

21

20

19

18

17

16

CURRENT_DST_ADDR [23:16]

15

14

13

12

11

10

9

8

CURRENT_DST_ADDR [15:8]

7

6

5

4

3

2

1

0

CURRENT_DST_ADDR [7:0]

BITS

DESCRIPTIONS

[31:0] CURRENT_DST_ADDR

The 32-bit Current Destination Address indicates the

destination address where the GDMA transfer is just

occurring. During a block transfer, the GDMA determines

the successive destination addresses by adding to or

subtracting from the destination base address. Depending

on the settings you make to the control register, the current

destination address will remain the same or will be

incremented or decremented.

Channel 0/1 Current Transfer Count Register (GDMA_CTCNT0,

GDMA_CTCNT1)

The Current transfer count register indicates the number of transfer being performed.

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET

VALUE

GDMA_CTCNT0 0xFFF0_4018 R

Channel 0 Current Transfer Count Register

0x0000_0000

GDMA_CTCNT1 0xFFF0_4038 R

Channel 1 Current Transfer Count Register

0x0000_0000