Rainbow Electronics W90N745CDG User Manual

Page 277

W90N745CD/W90N745CDG

- 272 -

Continued.

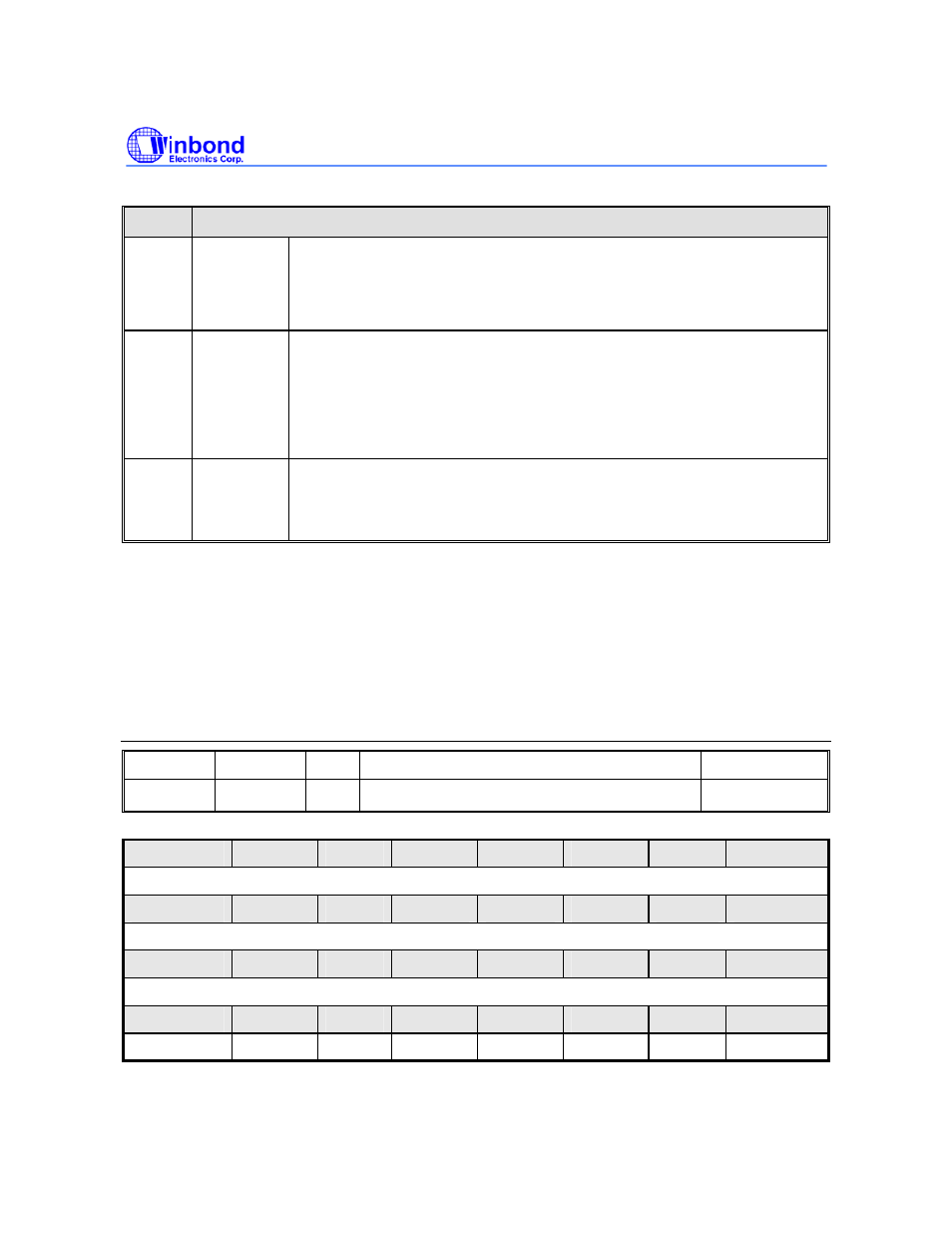

BITS

DESCRIPTIONS

[2] PEI

Parity Error Indicator

This bit is set to logic 1 whenever the received character does not have a

valid "parity bit", and is reset whenever the CPU reads the contents of the

LSR.

[1] OEI

Overrun Error Indicator

An overrun error will occur only after the RX FIFO is full and the next

character has been completely received in the shift register. The character

in the shift register is overwritten, but it is not transferred to the RX FIFO.

OE is indicated to the CPU as soon as it happens and is reset whenever

the CPU reads the contents of the LSR.

[0] RFDR

RX FIFO Data Ready

0 = RX FIFO is empty

1 = RX FIFO contains at least 1 received data word.

LSR [4:2] (BII, FEI, PEI) are revealed to the CPU when its associated character is at the top of the RX

FIFO. These three error indicators are reset whenever the CPU reads the contents of the LSR.

LSR [4:1] (BII, FEI, PEI, OEI) are the error conditions that produce a "receiver line status interrupt"

(Irpt_RLS) when IER [2]=1. Reading LSR clears Irpt_RLS. Writing LSR is a null operation (not

suggested)

UART Modem Status Register (UART_MSR)

REGISTER OFFSET R/W

DESCRIPTION

RESET

VALUE

UART_MSR

0x18 R

MODEM Status Register (Optional)

0x0000_0000

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved

7

6

5

4

3

2

1

0

Reserved Reserved

DSR#

Reserved

Reserved

Reserved

DDSR

Reserved