Rainbow Electronics W90N745CDG User Manual

Page 34

W90N745CD/W90N745CDG

Publication Release Date: September 22, 2006

-

29

-

Revision

A2

Big endian

In Big endian format, the W90N745 stores the most significant byte of a word at the lowest numbered

byte, and the least significant byte at the highest-numbered byte. So the byte at address 0 of the memory

system connects to data lines 31 through 24.

For a word aligned address A, Figure 6.2.3 shows how the half-word at addresses A and A+2, and the

bytes at addresses A, A+1, A+2, and A+3 map on to each other when the D14 pin is Low.

15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

Half-word at address A

Half-word at address A+2

Byte at address A

Byte at address A+1

Byte at address A+2

Byte at address A+3

Figure 6.2.3 Big endian addresses of bytes and half-words within half words

6.2.4.2. Connection of External Memory with Various Data Width

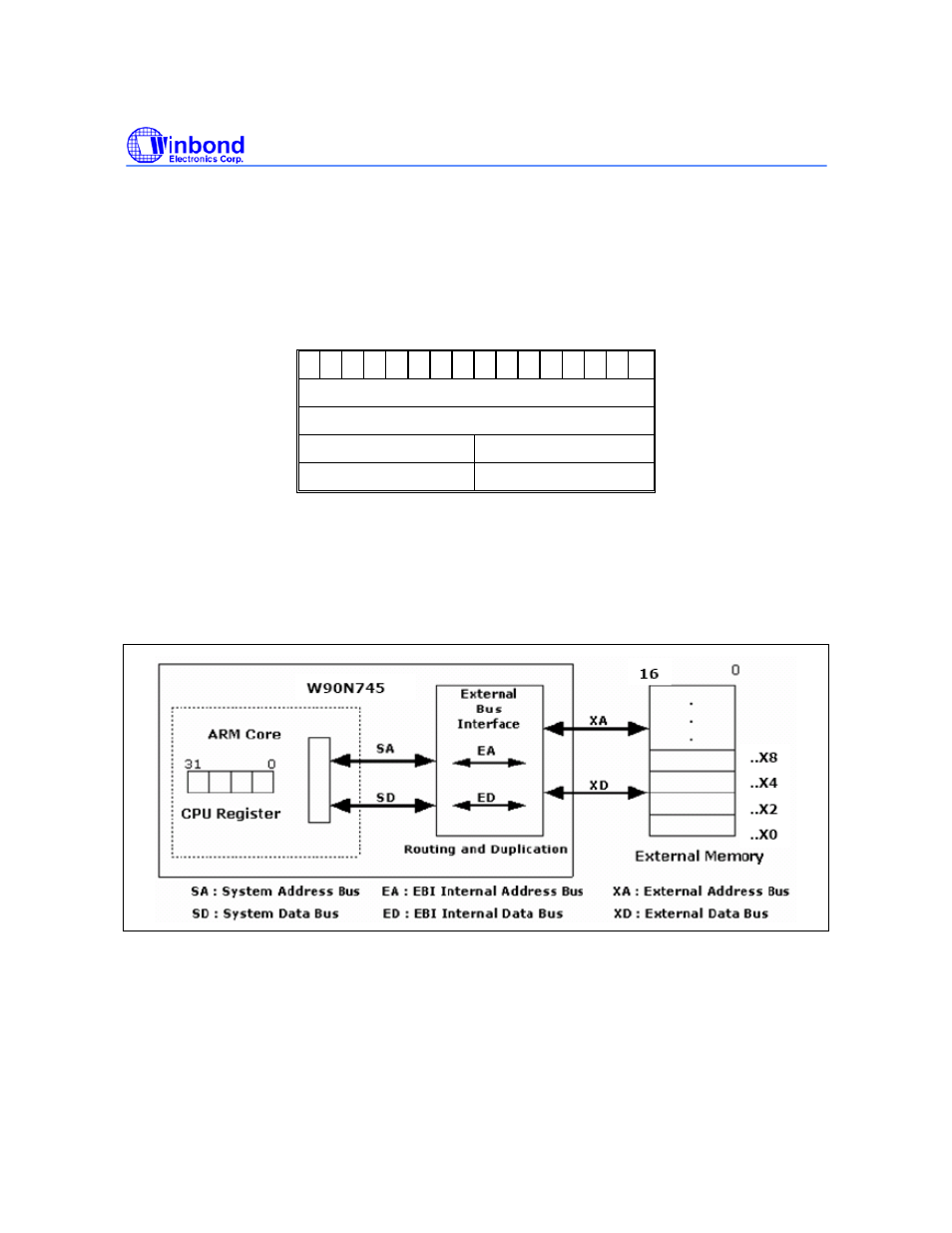

The system diagram for W90N745 connecting with the external memory is shown in Figure 6.2.4. Below

tables (Table 6.2.3 through Table 6.2.14) show the program/data path between CPU register and the

external memory using little / big endian and word/half-word/byte access.

Figure 6.2.4 Address/Data bus connection with external memory