Rainbow Electronics W90N745CDG User Manual

Page 147

W90N745CD/W90N745CDG

- 142 -

Continued.

BITS

DESCRIPTIONS

[0] RXINTR

The Receive Interrupt indicates the Rx interrupt status.

If RXINTR high and its corresponding enable bit, EnRXINTR of

MISTA register, is also high indicates the EMC generates Rx

interrupt to CPU. If RXINTR is high but EnRXINTR of MISTA is

disabled, no Rx interrupt is generated.

The RXINTR is logic OR result of the bits 1~14 in MISTA register

do logic AND with the corresponding bits in MIEN register. In

other words, if one of the bits 1~14 in MISTA register is high and

its corresponding enable bit in MIEN register is also enabled, the

RXINTR will be high.

Because the RXINTR is a logic OR result, clears bits 1~14 of

MISTA register makes RXINTR be cleared, too.

1’b0: No status of bits 1~14 in MISTA is set or no enable of bits

1~14 in MIEN is turned on.

1’b1: At least one status of bits 1~14 in MISTA is set and its

corresponding enable bit is turned on.

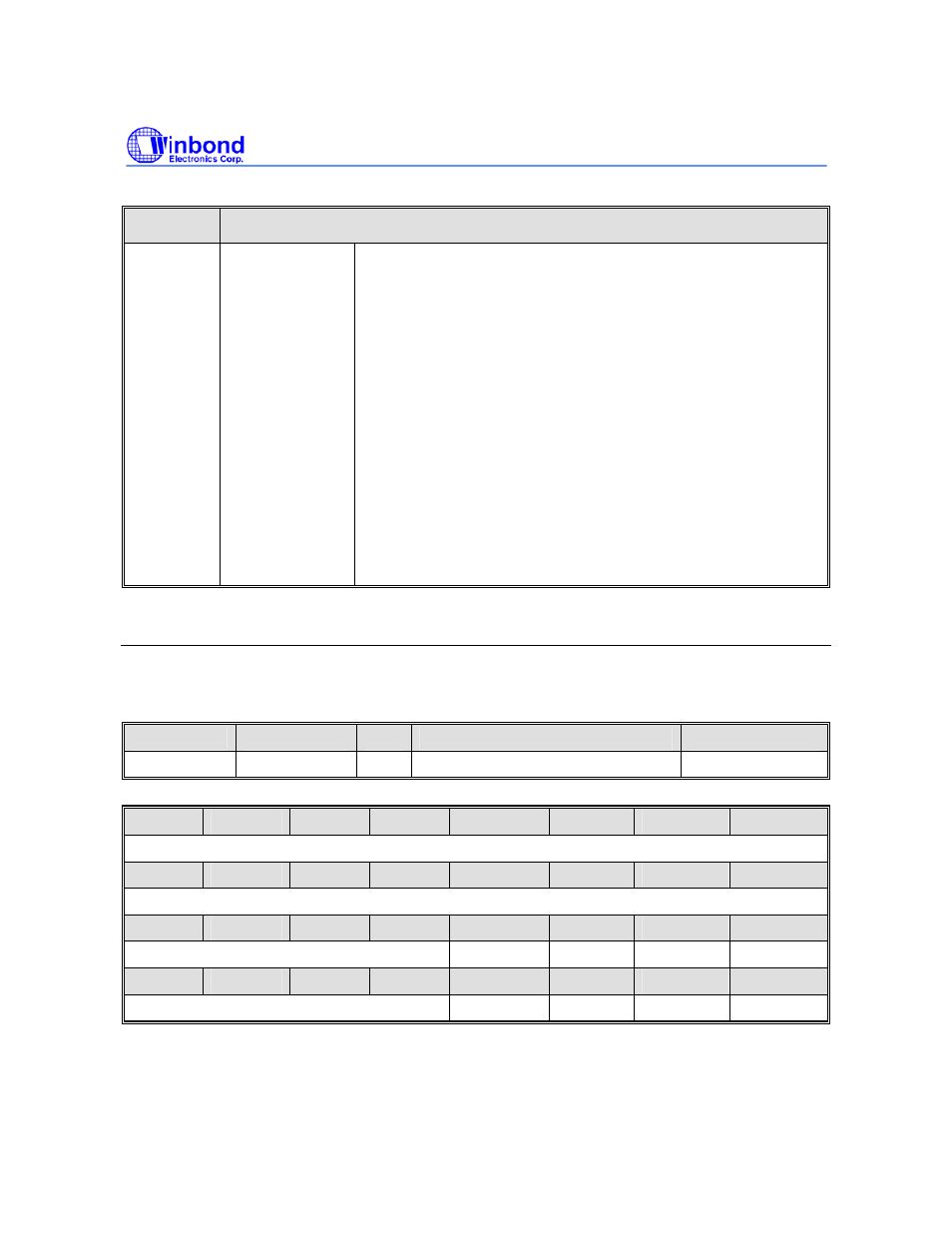

MAC General Status Register (MGSTA)

The MGSTA also keeps the statuses of EMC. But the statuses in the MGSTA will not trigger any

interrupt. The MGSTA is a write clear register and write 1 to corresponding bit clears the status.

REGISTER

ADDRESS

R/W

DESCRIPTION

RESET VALUE

MGSTA

0xFFF0_30B4

R/W

MAC General Status Register

0x0000_0000

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved TXHA

SQE

PAU

DEF

7

6

5

4

3

2

1

0

CCNT Reserved

RFFull

RXHA

CFR