Rainbow Electronics W90N745CDG User Manual

Page 137

W90N745CD/W90N745CDG

- 132 -

Continued.

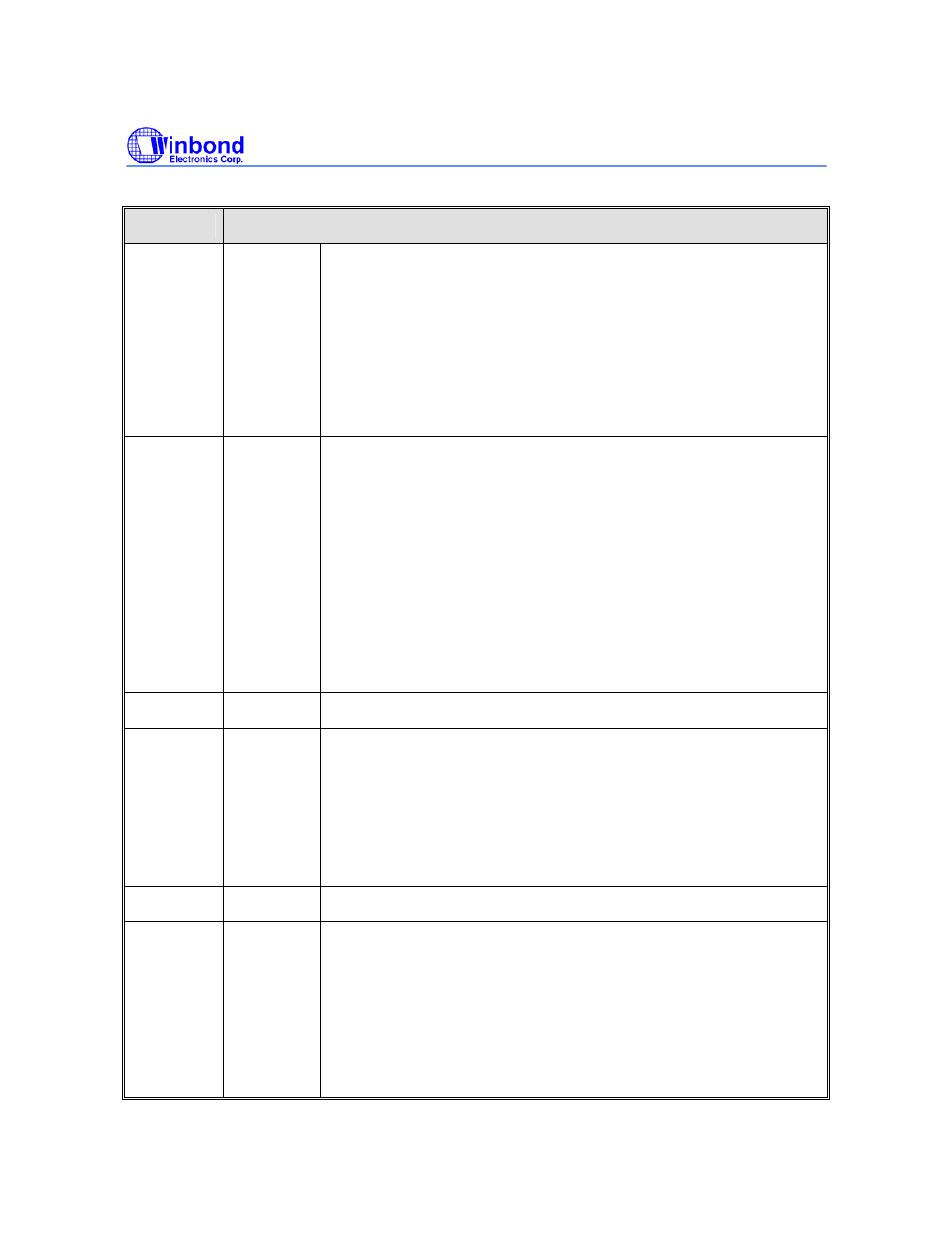

BITS

DESCRIPTIONS

[17] EnTXEMP

The Enable Transmit FIFO Underflow Interrupt controls the TXEMP

interrupt generation. If TXEMP of MISTA register is set, and both

EnTXEMP and EnTXINTR are enabled, the EMC generates the Tx

interrupt to CPU. If EnTXEMP or EnTXINTR is disabled, no Tx interrupt

is generated to CPU even the TXEMP of MISTA register is set.

1’b0: TXEMP of MISTA register is masked from Tx interrupt

generation.

1’b1: TXEMP of MISTA register can participate in Tx interrupt

generation.

[16]

EnTXINTR

The EnTXINTR controls the Tx interrupt generation.

If Enable Transmit Interrupt is enabled and TXINTR of MISTA

register is high, EMC generates the Tx interrupt to CPU. If EnTXINTR

is disabled, no Tx interrupt is generated to CPU even the status bits

17~24 of MISTA are set and the corresponding bits of MIEN are

enabled. In other words, if S/W wants to receive Tx interrupt from

EMC, this bit must be enabled. And, if S/W doesn’t want to receive any

Tx interrupt from EMC, disables this bit.

1’b0: TXINTR of MISTA register is masked and Tx interrupt generation

is disabled.

1’b1: TXINTR of MISTA register is unmasked and Tx interrupt

generation is enabled.

[15] Reserved

--

[14] EnCFR

The Enable Control Frame Receive Interrupt controls the CFR

interrupt generation. If CFR of MISTA register is set, and both EnCFR

and EnTXINTR are enabled, the EMC generates the Rx interrupt to

CPU. If EnCFR or EnTXINTR is disabled, no Rx interrupt is generated

to CPU even the CFR of MISTA register is set.

1’b0: CFR of MISTA register is masked from Rx interrupt generation.

1’b1: CFR of MISTA register can participate in Rx interrupt generation.

[13:12] Reserved

--

[11] EnRxBErr

The Enable Receive Bus Error Interrupt controls the RxBerr interrupt

generation. If RxBErr of MISTA register is set, and both EnRxBErr and

EnTXINTR are enabled, the EMC generates the Rx interrupt to CPU. If

EnRxBErr or EnTXINTR is disabled, no Rx interrupt is generated to

CPU even the RxBErr of MISTA register is set.

1’b0: RxBErr of MISTA register is masked from Rx interrupt generation.

1’b1: RxBErr of MISTA register can participate in Rx interrupt

generation.