Rainbow Electronics W90N745CDG User Manual

Page 347

W90N745CD/W90N745CDG

Publication Release Date: September 22, 2006

-

343

-

Revision

A2

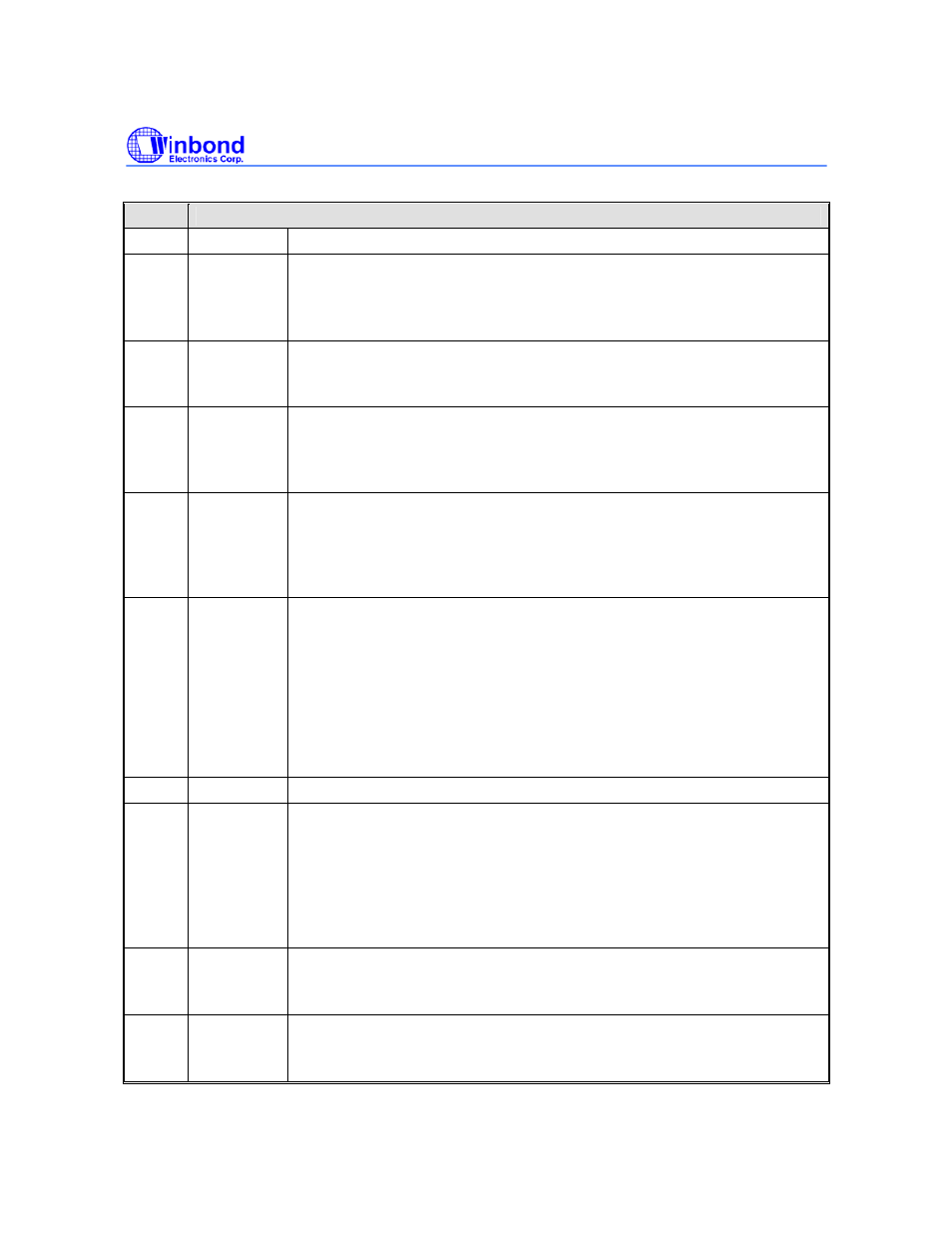

BITS

DESCRIPTIONS

[31:12]

Reserved Reserved

[11]

I

2

C_RxAC

K

Received Acknowledge From Slave (Read only)

This flag represents acknowledge from the addressed slave.

0 = Acknowledge received (ACK).

1 = Not acknowledge received (NACK).

[10]

I

2

C_BUSY

I

2

C Bus Busy (Read only)

0 = After STOP signal detected.

1 = After START signal detected.

[9]

I

2

C_AL

Arbitration Lost (Read only)

This bit is set when the I

2

C core lost arbitration. Arbitration is lost when:

A STOP signal is detected, but no requested.

The master drives SDA high, but SDA is low.

[8]

I

2

C_TIP

Transfer In Progress (Read only)

0 = Transfer complete.

1 = Transferring data.

NOTE: When a transfer is in progress, you will not allow writing to any

register of the I

2

C master core except SWR.

[5:4]

Tx_NUM

Transmit Byte Counts

These two bits represent how many bytes are remained to transmit. When a

byte has been transmitted, the Tx_NUM will decrease 1 until all bytes are

transmitted (Tx_NUM = 0x0) or NACK received from slave. Then the

interrupt signal will assert if IE was set.

0x0 = Only one byte is left for transmission.

0x1 = Two bytes are left to for transmission.

0x2 = Three bytes are left for transmission.

0x3 = Four bytes are left for transmission.

[3]

Reserved Reserved

[2]

IF

Interrupt Flag

The Interrupt Flag is set when:

Transfer has been completed.

Transfer has not been completed, but slave responded NACK (in multi-byte

transmit mode).

Arbitration is lost.

NOTE: This bit is read only, but can be cleared by writing 1 to this bit.

[1]

IE

Interrupt Enable

0 = Disable I

2

C Interrupt.

1 = Enable I

2

C Interrupt.

[0]

I

2

C_EN

I

2

C Core Enable

0 = Disable I

2

C core, serial bus outputs are controlled by SDW/SCW.

1 = Enable I

2

C core, serial bus outputs are controlled by I

2

C core.