Rainbow Electronics W90N745CDG User Manual

Page 276

W90N745CD/W90N745CDG

Publication Release Date: September 22, 2006

-

271

-

Revision

A2

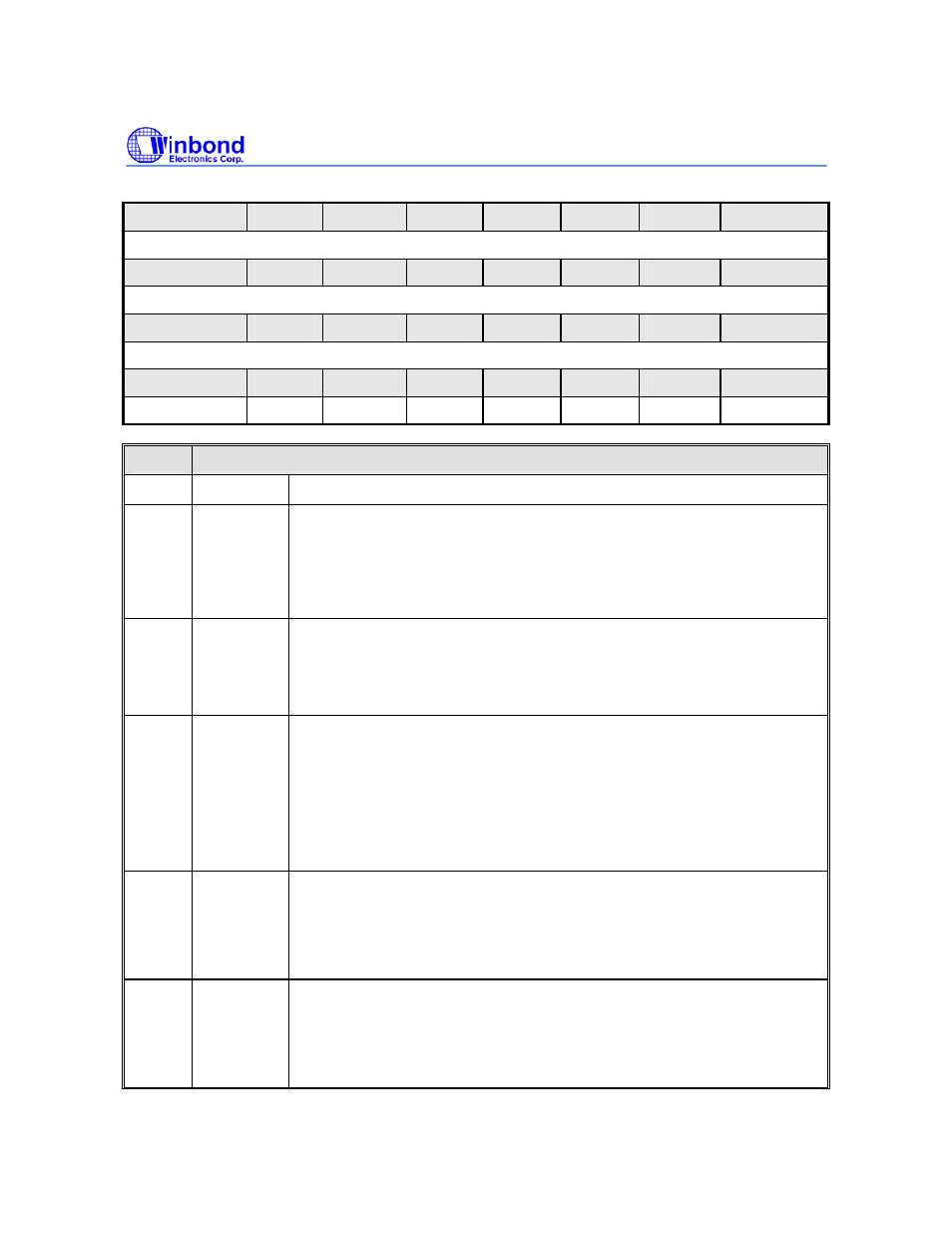

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved

7

6

5

4

3

2

1

0

ERR_RX TE

THRE

BII FEI PEI OEI RFDR

BITS

DESCRIPTIONS

[31:8] Reserved

-

[7] ERR_RX

RX FIFO Error

0 = RX FIFO works normally

1 = There is at least one parity error (PE), framing error (FE), or break

indication (BI) in the FIFO. ERR_RX is cleared when CPU reads the LSR and

if there are no subsequent errors in the RX FIFO.

[6] TE

Transmitter Empty

0 = Either Transmitter Holding Register (THR - TX FIFO) or Transmitter Shift

Register (TSR) are not empty.

1 = Both THR and TSR are empty.

[5] THRE

Transmitter Holding Register Empty

0 = THR is not empty.

1 = THR is empty.

THRE is set when the last data word of TX FIFO is transferred to Transmitter

Shift Register (TSR). The CPU resets this bit when the THR (or TX FIFO) is

loaded. This bit also causes the UART to issue an interrupt (Irpt_THRE) to the

CPU when IER [1]=1.

[4] BII

Break Interrupt Indicator

This bit is set to a logic 1 whenever the received data input is held in the

"spacing state" (logic 0) for longer than a full word transmission time (that is,

the total time of "start bit" + data bits + parity + stop bits) and is reset

whenever the CPU reads the contents of the LSR.

[3] FEI

Framing Error Indicator

This bit is set to logic 1 whenever the received character does not have a

valid "stop bit" (that is, the stop bit following the last data bit or parity bit is

detected as a logic 0), and is reset whenever the CPU reads the contents of

the LSR.