Rainbow Electronics W90N745CDG User Manual

Page 174

W90N745CD/W90N745CDG

Publication Release Date: September 22, 2006

-

169

-

Revision

A2

Interrupt Processing

Interrupts are the communication method for HC-initiated communication with the Host Controller

Driver. There are several events that may trigger an interrupt from the Host Controller. Each specific

event sets a specific bit in the HcInterruptStatus register.

Host Controller Bus Master

The Host Controller Bus Master is the central block in the data path. The Host Controller Bus Master

coordinates all access to the AHB Interface. There are two sources of bus mastering within Host

Controller: the List Processor and the Data Buffer Engine.

Data Buffer

The Data Buffer serves as the data interface between the Bus Master and the SIE. It is a combination

of a 64-byte latched based bi-directional asynchronous FIFO and a single Dword AHB Holding

Register.

6.7.1.3. USB Interface

The USB interface includes the integrated Root Hub with two external ports, Port 1 and Port 2 as well

as the Serial Interface Engine (SIE) and USB clock generator. The interface combines responsibility

for executing bus transactions requested by the HC as well as the hub and port management

specified by USB.

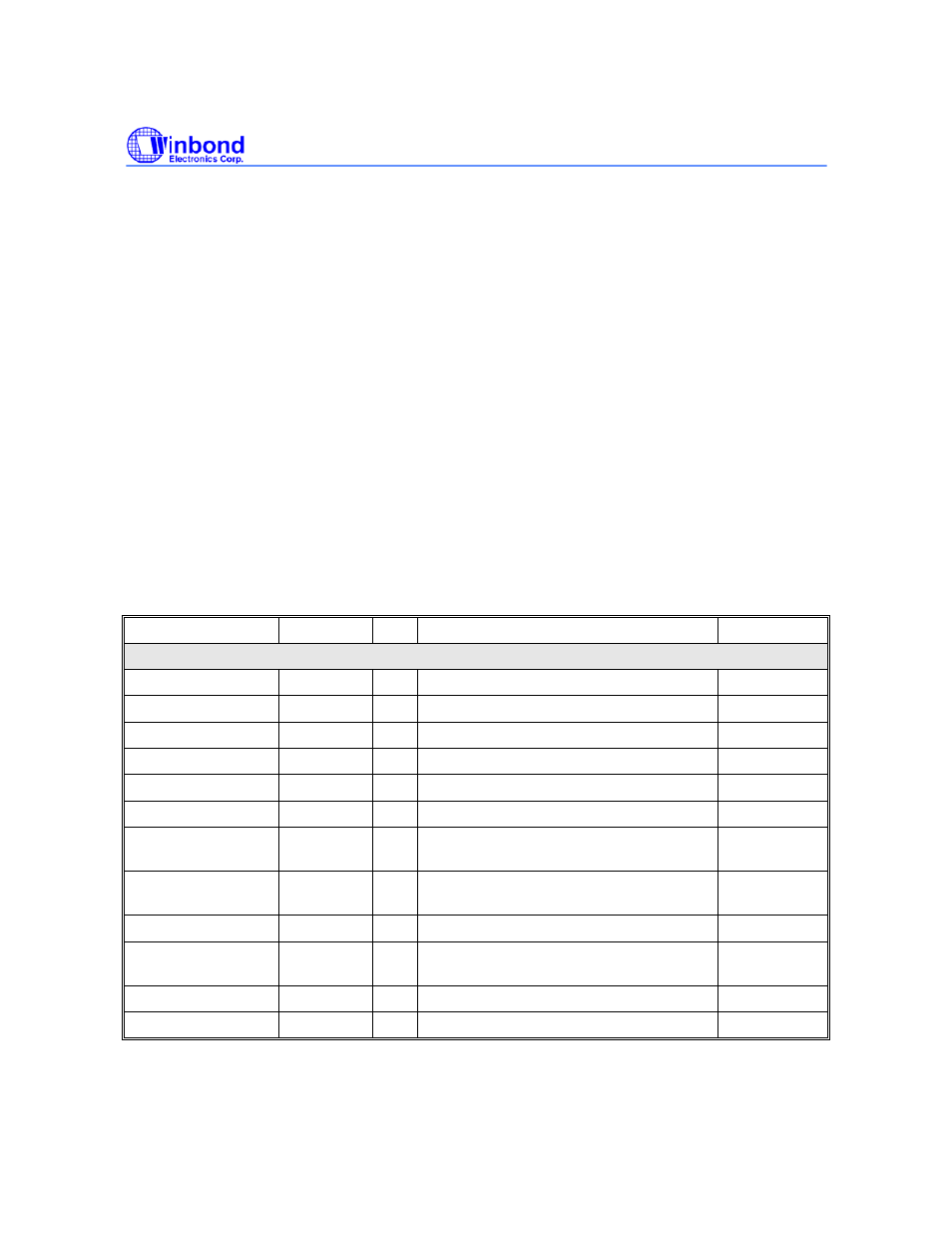

6.7.2 USB Host Controller Registers Map

REGISTER ADDRESS

R/W

DESCRIPTION

RESET

VALUE

OpenHCI Registers

HcRevision 0xFFF0_5000

R Host Controller Revision Register

0x0000_0010

HcControl 0xFFF0_5004

R/W Host Controller Control Register

0x0000_0000

HcCommandStatus 0xFFF0_5008

R/W Host Controller Command Status Register 0x0000_0000

HcInterruptStatus 0xFFF0_500C

R/W Host Controller Interrupt Status Register

0x0000_0000

HcInterruptEnbale 0xFFF0_5010

R/W Host Controller Interrupt Enable Register

0x0000_0000

HcInterruptDisbale 0xFFF0_5014

R/W Host Controller Interrupt Disable Register 0x0000_0000

HcHCCA 0xFFF0_5018

R/W

Host Controller Communication Area

Register

0x0000_0000

HcPeriodCurrentED 0xFFF0_501C

R/W

Host Controller Period Current ED

Register

0x0000_0000

HcControlHeadED 0xFFF0_5020

R/W Host Controller Control Head ED Register 0x0000_0000

HcControlCurrentED 0xFFF0_5024

R/W

Host Controller Control Current ED

Register

0x0000_0000

HcBulkHeadEd 0xFFF0_5028

R/W Host Controller Bulk Head ED Register

0x0000_0000

HcBulkCurrentED 0xFFF0_502C

R/W Host Controller Bulk Current ED Register

0x0000_0000