Functional description – Artesyn MVME2502 Installation and Use (April 2015) User Manual

Page 91

Functional Description

MVME2502 Installation and Use (6806800R96E)

91

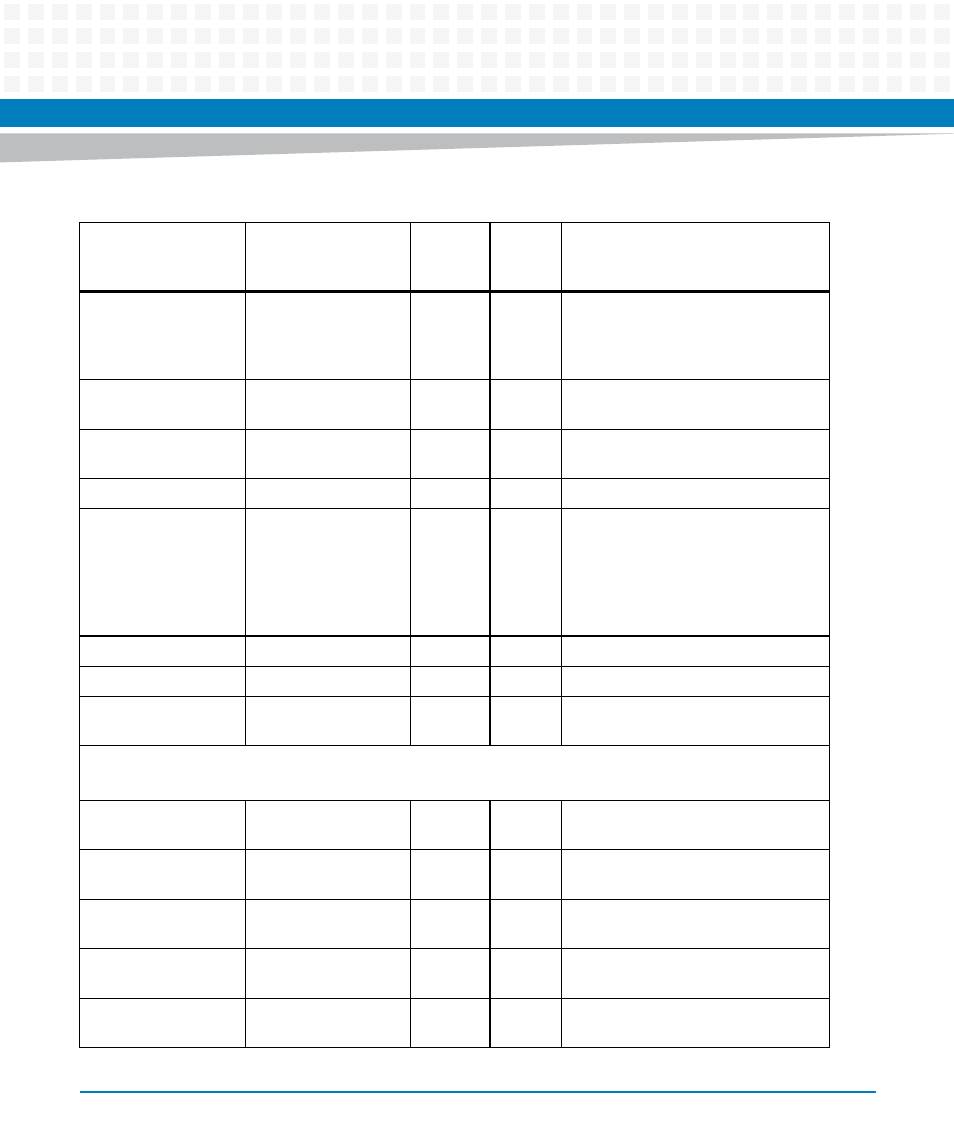

LA26

cfg_ddr_speed

Yes

1

DDR Controller complex clock

frequency (same as DDR rate) is

greater than or equal to 500 MHZ

(default)

LVDD_VSEL

Yes

1

eTSEC, ethernet management, 1588

interfaces = 2.5V

BVD_VSEL[0:1]

Yes

11

Local bus and GPIO[8:15] interfaces =

3.3V

CVDD_VSEL[0:1]

Yes

00

USB, eSDHC, SPI interface = 3.3V

LA[20:22]

UART_SOUT[0]

TRIG_OUT

MSRCID[1]

MSRCID[4]

DMA1_DDONE_B[0]

cfg_en_use[0:7]

Yes

111111

11

default

TSEC2_TXD1

cfg_dram_type

Yes

1

DDR3 SDRAM selected 1.5V (default)

TSEC2_TXD5

cfg_sdhc_cd_pol_sel

Yes

1

SDHC polarity detect = not inverted

TSEC1_TXD[6:4]

TSEC1_TX_ER

cfg_rom_loc[0:3]

Yes

0110

Location of boot ROM = SPI FLASH

For the following options, no strapping options provided. They are only listed for reference.

LGPL1

cfg_sgmii2

No

1

eTSEC2 interface operates in parallel

interface mode (default)

TSEC_1588_ALARM_

OUT2

cfg_sgmii3

No

1

eTSEC3 interface operates in parallel

interface mode (default)

TSEC_1588_ALARM_

OUT1

cfg_srds_refclk

No

1

100MHz SERDES ref clock for PCIE

(default)

LWE1/LBS1 LA[18:19]

cfg_host_agt[0:2]

No

111

Processor acts as the host root

complex for all PCIE busses(default)

TSEC2_TXD[4:2]

cfg_device_ID[7:5]

No

111

Rapid IO interface not used => default

values used

Table 4-2 P2020 Strapping Options (continued)

Functional Signal

Name

Reset Configuration

Name

Config

Resistor

Options

Default

Value

Description

- MVME2502 Installation and Use (August 2014) MVME2500 Installation and Use Manual (February 2014) MVME2500 ECC Installation and Use (August 2014) MVME2500 Installation and Use (April 2015) MVME2500 Installation and Use Manual (March 2015) MVME2502 Installation and Use (April 2014) MVME2502 Installation and Use (December 2014)