Functional description – Artesyn MVME2502 Installation and Use (April 2015) User Manual

Page 90

Functional Description

MVME2502 Installation and Use (6806800R96E)

90

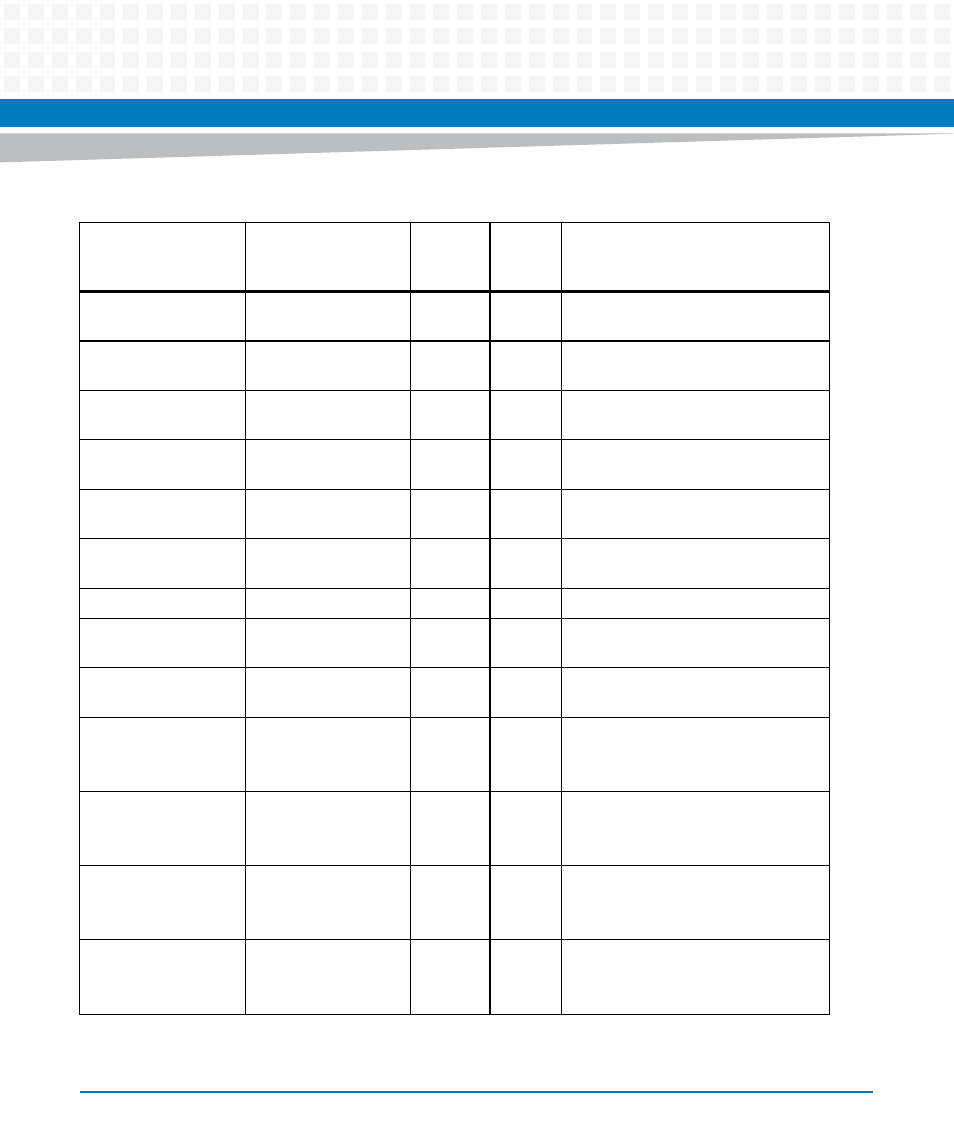

DMA2_DDONE0

cfg_ddr_debug

Yes

1

Debug information is not driven on

ECC pins (default)

EC_MDC

cfg_tsec_reduce

Yes

0

eTSEC1 and eTSEC2 Ethernet

interfaces operate in RGMII mode

TSEC1_TXD[0,7]

cfg_tsec1_prctcl[0:1] Yes

10

The eTSEC1 controller operates using

the RGMII protocol

TSEC2_TXD[0,7]

cfg_tsec2_prctcl[0:1] Yes

10

The eTSEC2 controller operates using

the RGMII protocol

UART_RTS0,UART_RT

S1

cfg_tsec3_prctcl[0:1] Yes

10

The eTSEC3 controller operates using

the RGMII protocol

TSEC1_TXD[3:1]

TSEC2_TX_ERR

cfg_io_ports[0:3]

Yes

0010

PCIE1=1x, PCIE2=1x, PCI3=2x

MSRCID0

cfg_elbc_ecc

Yes

0

eLBC ECC checking is disabled

LA28

cfg_sys_speed

Yes

1

SYSCLK is at or above 66MHz

(default)

LA23

cfg_plat_speed

Yes

1

Platform clock is at or above 333MHz

(default)

LA24

cfg_core0_speed

Yes

1

ENP1:

Core0 clock frequency is greater than

1000MHz

0

ENP2:

Core0 clock frequency is less than or

equal to 1000MHz

LA25

cfg_core1_speed

Yes

1

ENP1:

Core1 clock frequency is greater than

1000MHz

0

ENP2:

Core1 clock frequency is less than or

equal to 1000MHz

Table 4-2 P2020 Strapping Options (continued)

Functional Signal

Name

Reset Configuration

Name

Config

Resistor

Options

Default

Value

Description

- MVME2502 Installation and Use (August 2014) MVME2500 Installation and Use Manual (February 2014) MVME2500 ECC Installation and Use (August 2014) MVME2500 Installation and Use (April 2015) MVME2500 Installation and Use Manual (March 2015) MVME2502 Installation and Use (April 2014) MVME2502 Installation and Use (December 2014)