5 programmable logic device (pld) registers, 1 pld revision register, Table 5-4 – Artesyn MVME2502 Installation and Use (April 2015) User Manual

Page 114: Pld revision register

Memory Maps and Registers

MVME2502 Installation and Use (6806800R96E)

114

5.5

Programmable Logic Device (PLD) Registers

5.5.1

PLD Revision Register

The MVME2502 provides a PLD revision register that is read by the system software to

determine the current version of the timers/registers PLD.

Global Utilities CCSR

0xffee0000 0xffee0fff

4 KB

L2 Cache Mem

0xf0f80000 0xf0ffffff

512 KB

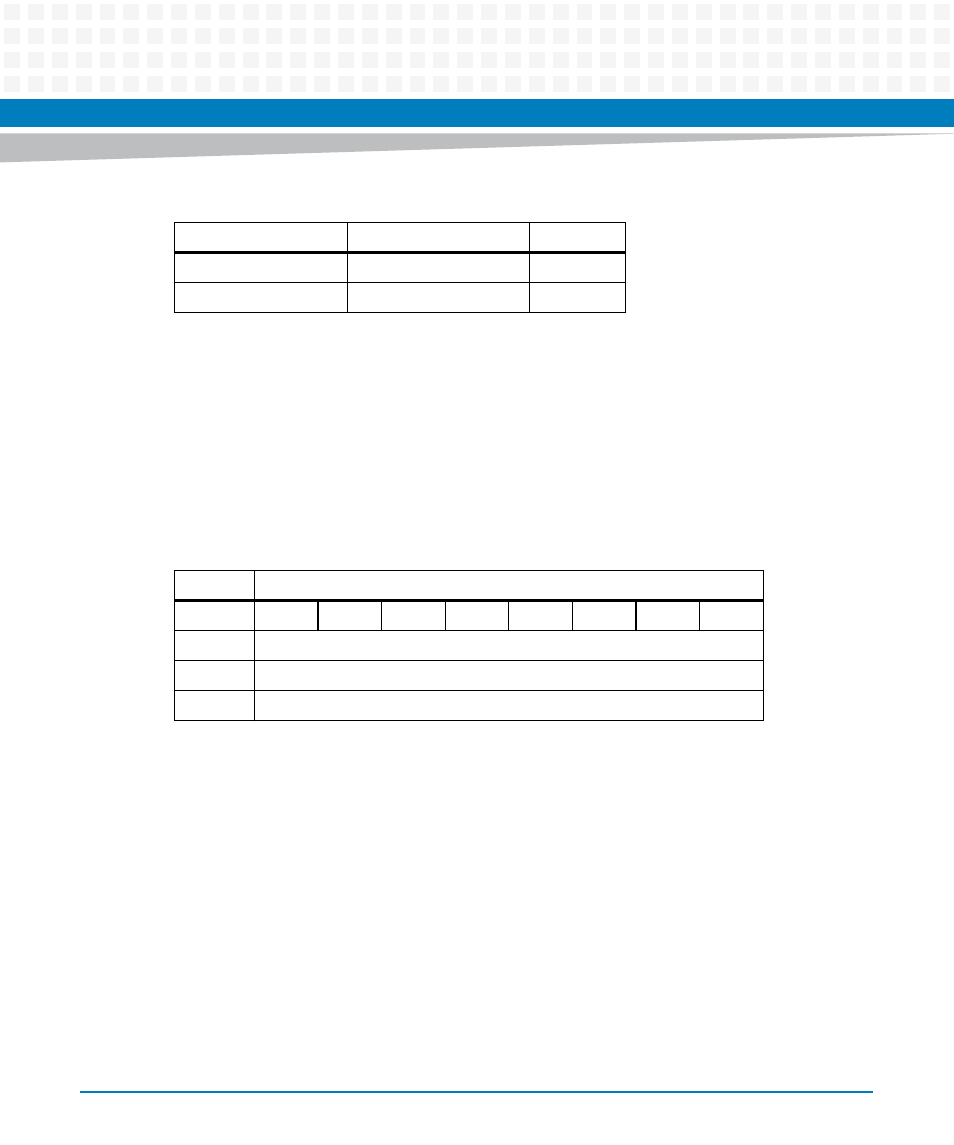

Table 5-3 Linux Devices Memory Map (continued)

Device Memory Range

Memory Area

Size

Table 5-4 PLD Revision Register

REG

PLD Revision Register - 0xFFDF0000

Bit

7

6

5

4

3

2

1

0

Field

PLD_REV

OPER

R

RESET

0x01

Field Description

PLD_REV

8-bit field containing the current timer/register PLD revision. The

revision number starts at 01.

This manual is related to the following products:

- MVME2502 Installation and Use (August 2014) MVME2500 Installation and Use Manual (February 2014) MVME2500 ECC Installation and Use (August 2014) MVME2500 Installation and Use (April 2015) MVME2500 Installation and Use Manual (March 2015) MVME2502 Installation and Use (April 2014) MVME2502 Installation and Use (December 2014)