Programming model – Artesyn MVME2502 Installation and Use (April 2015) User Manual

Page 148

Programming Model

MVME2502 Installation and Use (6806800R96E)

148

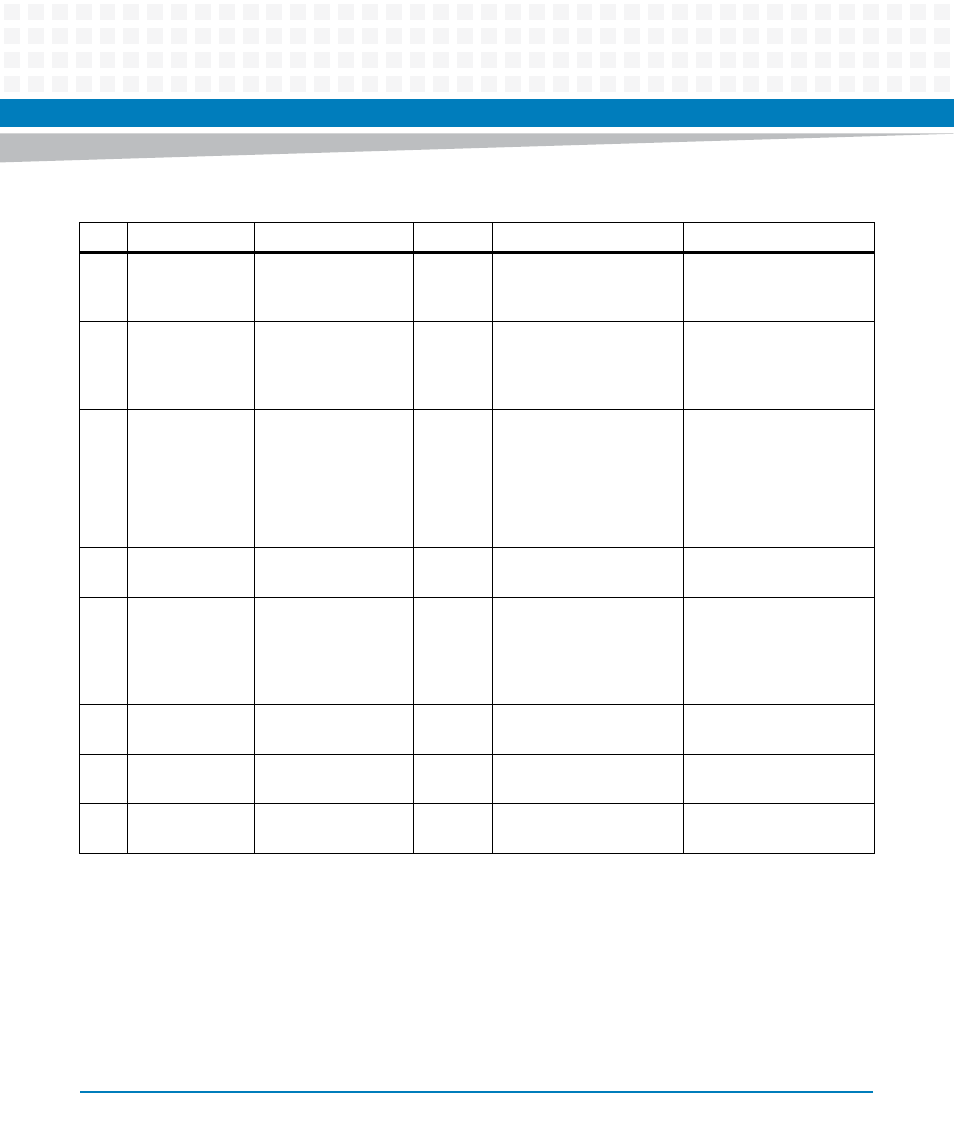

24

BOOT ROM

Location

TSEC1_TXD[6:4],

TSEC1_TX_ER

011X

On-chip boot ROM-SPI

configuration (x=0),

SDHC (x=1)

25

Host/Agent

Config

LWE1/LBS1,

LA[18:19]

111

The processor acts as the

host/root complex for all

PCI-E/Serial Rapid IO

interfaces (default).

26

I/O Port Select

TSEC1_TXD[3:1],

TSEC2_TX_ER

0010

PCI-E 1 (x1) (2.5 Gbps) -

SerDes lane 0

PCI-E 2 (x1) (2.5 Gbps) -

SerDes lane 2

PCI-E 3 (x2) (2.5 Gbps) -

SerDes lane 2-3

27

DDR SDRAM

TYPE

TSEC2_TXD1

1

DDR31.5 V. CKE low at

reset (default)

28

SerDes PLL Time

Out Enable

TRIG_OUT

1

Disable PLL lock time-out

counter. The power-on-

reset sequence waits

indefinitely for the SerDes

PLL to lock (default).

29

System Speed

LA[28]

1

SYSCLOCK is above 66

MHz

30

SDHC Card

Detect Polarity

TSEC2_TXD_5

1

Not Inverted

31

RAPID System

Size

Default

RapidIO is not used

Table 7-1 POR Configuration Settings (continued)

CONFIG

CONFIG PINS

CONFIG

SELECTION

REMARKS

- MVME2502 Installation and Use (August 2014) MVME2500 Installation and Use Manual (February 2014) MVME2500 ECC Installation and Use (August 2014) MVME2500 Installation and Use (April 2015) MVME2500 Installation and Use Manual (March 2015) MVME2502 Installation and Use (April 2014) MVME2502 Installation and Use (December 2014)