14 p2020 strapping pins, Table 4-2, P2020 strapping options – Artesyn MVME2502 Installation and Use (April 2015) User Manual

Page 89: Functional description

Functional Description

MVME2502 Installation and Use (6806800R96E)

89

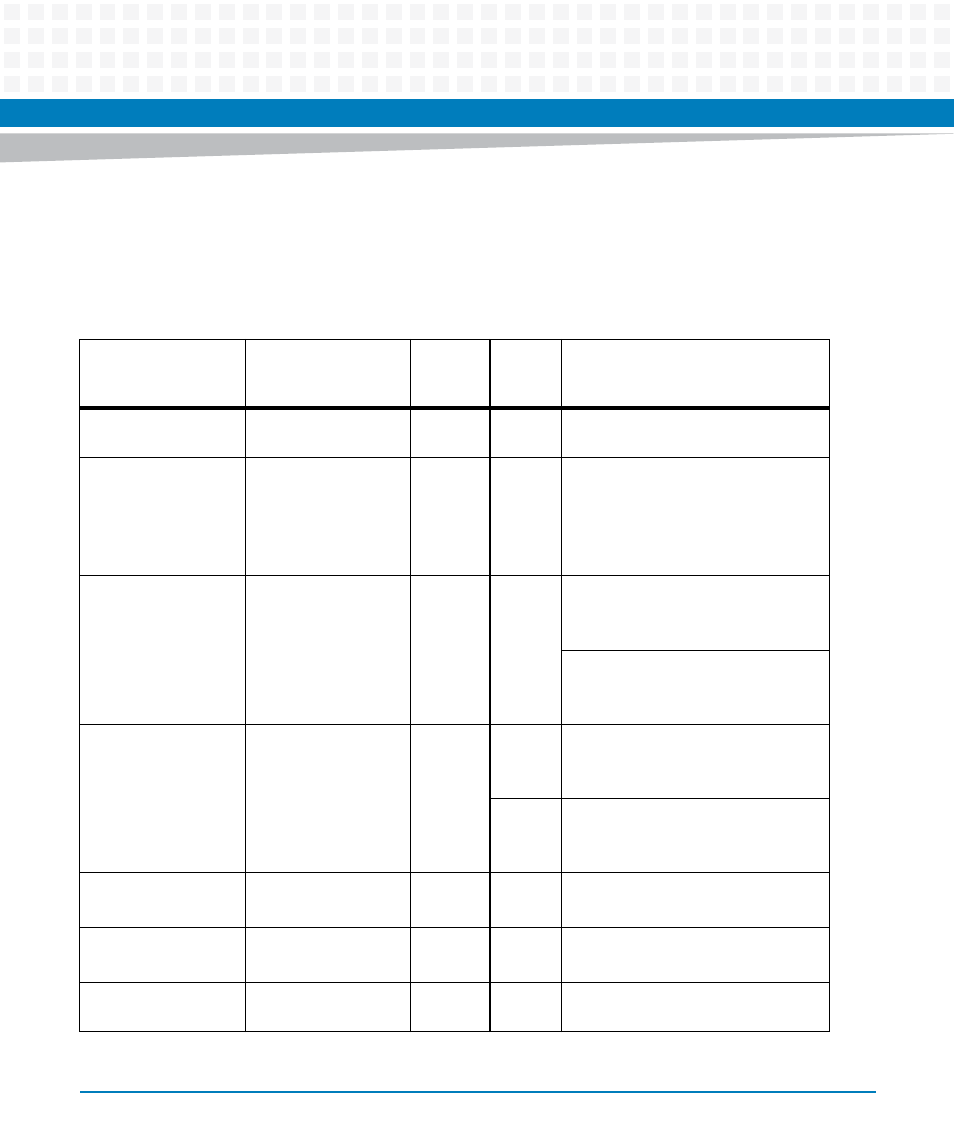

4.2.14 P2020 Strapping Pins

The following table lists all the P2020 strapping pins and the default configuration settings for

the MVME2502.

Table 4-2 P2020 Strapping Options

Functional Signal

Name

Reset Configuration

Name

Config

Resistor

Options

Default

Value

Description

LA[29:31]

cfg_sys_pii[0:2]

Yes

000

4:1 ratio CCB clock: SYSCLK

=100MHz, CCB=400Mhz

TSEC_1588_CLKOUT

TSEC_1588_PULSE_O

UT1

TSEC_1588_PULSE_O

UT2

cfg_ddr_pii[0:2]

Yes

011

8:1 ratio, DDRCLK=100MHz, DDRPLL

(data

rate) = 800MHz

LBCTL

LALE

LGPL2/LOE/LFRE

cfg_core0pii[0:2]

Yes

110

101

ENP1:

3:1 ratio, CCB clock= 400MHz, Core

clock=1200MHz

ENP2:

2.5:1 ratio, CCB clock= 400MHz, Core

clock=1000MHz

LWE0_N

UART_SOUT1

READY_P1

cfg_core1pii[0:2]

Yes

110

ENP1:

3:1 ratio, CCB clock= 400MHz, Core

clock=1200MHz

101

ENP2:

2.5:1 ratio, CCB clock= 400MHz, Core

clock=1000MHz

LA27

LA16

cfg_cup0_boot

cfg_cpu1_boot

Yes

10

CPU0 boot without waiting. CPU1

holdoff

LGPL3/LFW

PLGPL5

cfg_boot_seq[0:1]

Yes

11

Boot sequencer is disabled. No I2C

ROM is accessed (default)

DMA2_DACK0

cfg_mem_debug

Yes

1

DDR SDRAM controller debug info

driven to MSRCID/MDVAL (default)

- MVME2502 Installation and Use (August 2014) MVME2500 Installation and Use Manual (February 2014) MVME2500 ECC Installation and Use (August 2014) MVME2500 Installation and Use (April 2015) MVME2500 Installation and Use Manual (March 2015) MVME2502 Installation and Use (April 2014) MVME2502 Installation and Use (December 2014)