12 security engine (sec) 3.1, 13 common on-chip processor (cop), Functional description – Artesyn MVME2502 Installation and Use (April 2015) User Manual

Page 88

Functional Description

MVME2502 Installation and Use (6806800R96E)

88

4.2.12 Security Engine (SEC) 3.1

The integrated security engine of the P2020 is designed to off load intensive security functions

like key generation and exchange, authentication and bulk encryption from the processor core.

It includes eight different execution units where data flows in and out of an EU.

NOTE: The standard versions of the MVME2502 do not use the encryption enabled versions of

the P2020 processor.

4.2.13 Common On-Chip Processor (COP)

The COP is the debug interface of the QorIQ P2020 Processor. It allows a remote computer

system to access and control the internal operation of the processor. The COP interface

connects primarily through the JTAG and has additional status monitoring signals. The COP has

additional features like breakpoints, watch points, register and memory

examination/modification and other standard debugging features.

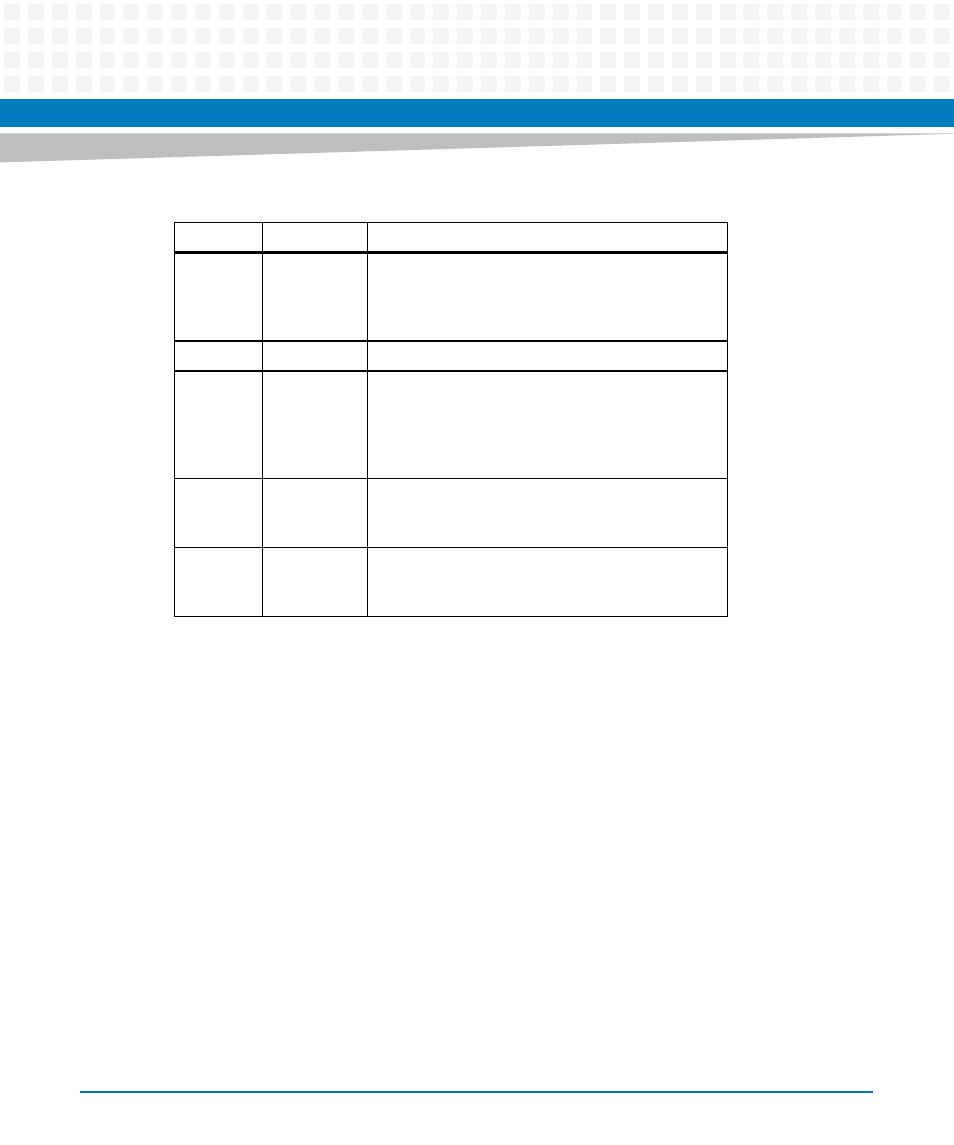

04

U29

Connected to INTA of the QUART. Programmed as

a discrete input or to generate IRQ11.

Also connected to pin P16 of the CPLD. (unused

input)

03

N24

Connected to pin P15of the CPLD

02

P29

Connected to Pin R16 of the CPLD. Programmed to

generate a IRQ09 interrupt to the CPU based on

contents of the CPLD GPIO2 interrupt register. For

more information see,

01

R26

Connected to INTA_N of the DS1337 Real Time

Clock (RTC). Programmed as a discrete input or to

generate IRQ08

00

R28

Connected to LED_P21[2] of the BCM5482S.

Programmed as a discrete input or to generate

IRQ07.

Table 4-1 P2020 GPIO Functions (continued)

GPIO bit

CPU Pin #

Function

- MVME2502 Installation and Use (August 2014) MVME2500 Installation and Use Manual (February 2014) MVME2500 ECC Installation and Use (August 2014) MVME2500 Installation and Use (April 2015) MVME2500 Installation and Use Manual (March 2015) MVME2502 Installation and Use (April 2014) MVME2502 Installation and Use (December 2014)