13 pld test register 1, Table 5-16, Pld test register 1 – Artesyn MVME2502 Installation and Use (April 2015) User Manual

Page 124

Memory Maps and Registers

MVME2502 Installation and Use (6806800R96E)

124

5.5.13 PLD Test Register 1

The MVME2502 PLD provides an 8-bit general purpose read/write register which is used by the

software for PLD testing or general status bit storage.

I2C_DEBUG_EN

I2C debug ports (I2C_1_D and I2C_1_C) enable

1 - Drive Enabled

0 - Drive Disabled

SERIAL_FLASH_WP

SPI devices write-protect register

0 - SPI FLASH writes enabled

1 - SPI FLASH writes disabled

I2C_1_D

I2C debug port-Data

0 - Driven Low

1 - HiZ

I2C_1_C

I2C debug port-Clock

0 - Driven Low

1 - HiZ

When SERIAL_FLASH_WP is set to "Low", this port will automatically read as low due to "AND"

connection between the two ports.

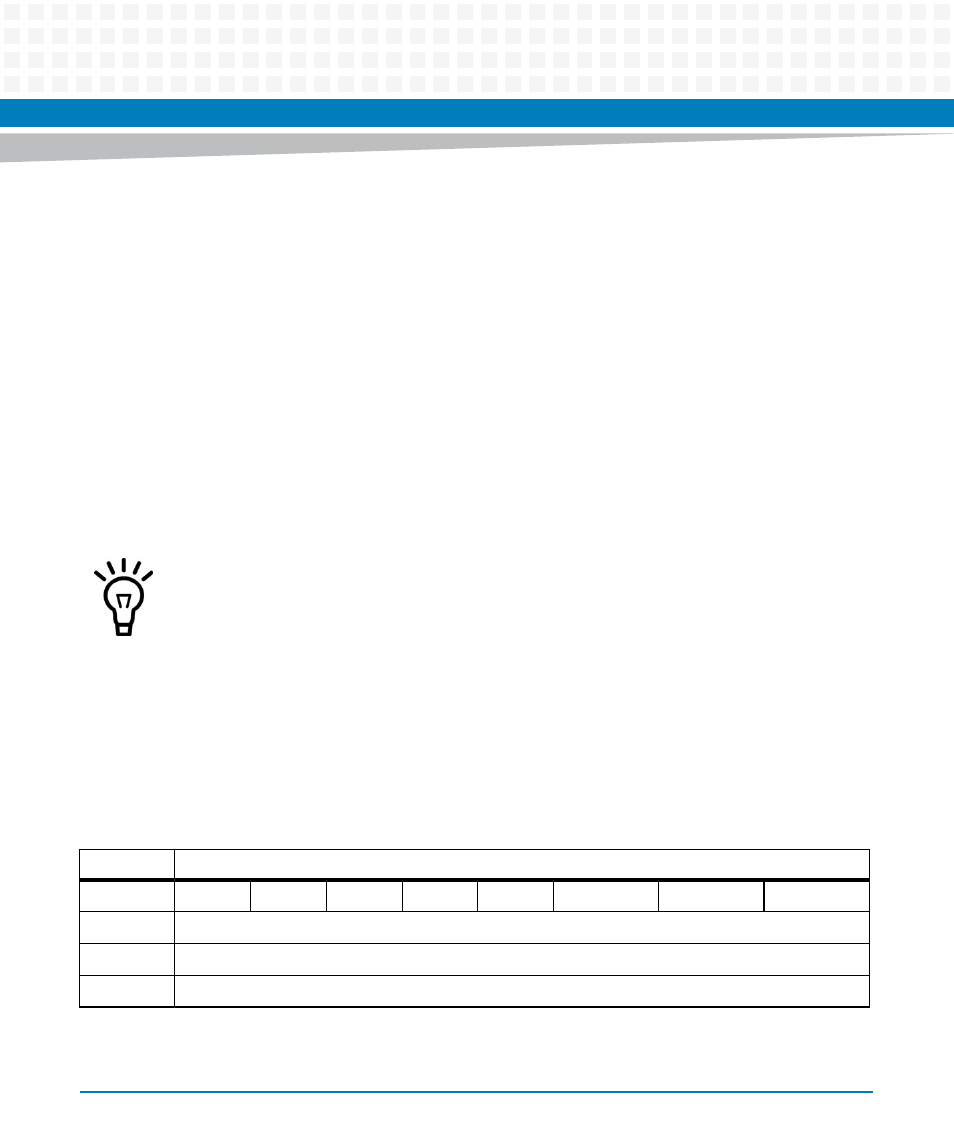

Table 5-16 PLD Test Register 1

REG

PLD Write Protect I2C Debug- 0xFFDF0095

Bit

7

6

5

4

3

2

1

0

Field

TEST_REG1

OPER

R/W

RESET

00

- MVME2502 Installation and Use (August 2014) MVME2500 Installation and Use Manual (February 2014) MVME2500 ECC Installation and Use (August 2014) MVME2500 Installation and Use (April 2015) MVME2500 Installation and Use Manual (March 2015) MVME2502 Installation and Use (April 2014) MVME2502 Installation and Use (December 2014)