1 system clock, Table 7-7, System clock – Artesyn MVME2502 Installation and Use (April 2015) User Manual

Page 154: Programming model

Programming Model

MVME2502 Installation and Use (6806800R96E)

154

7.7.1

System Clock

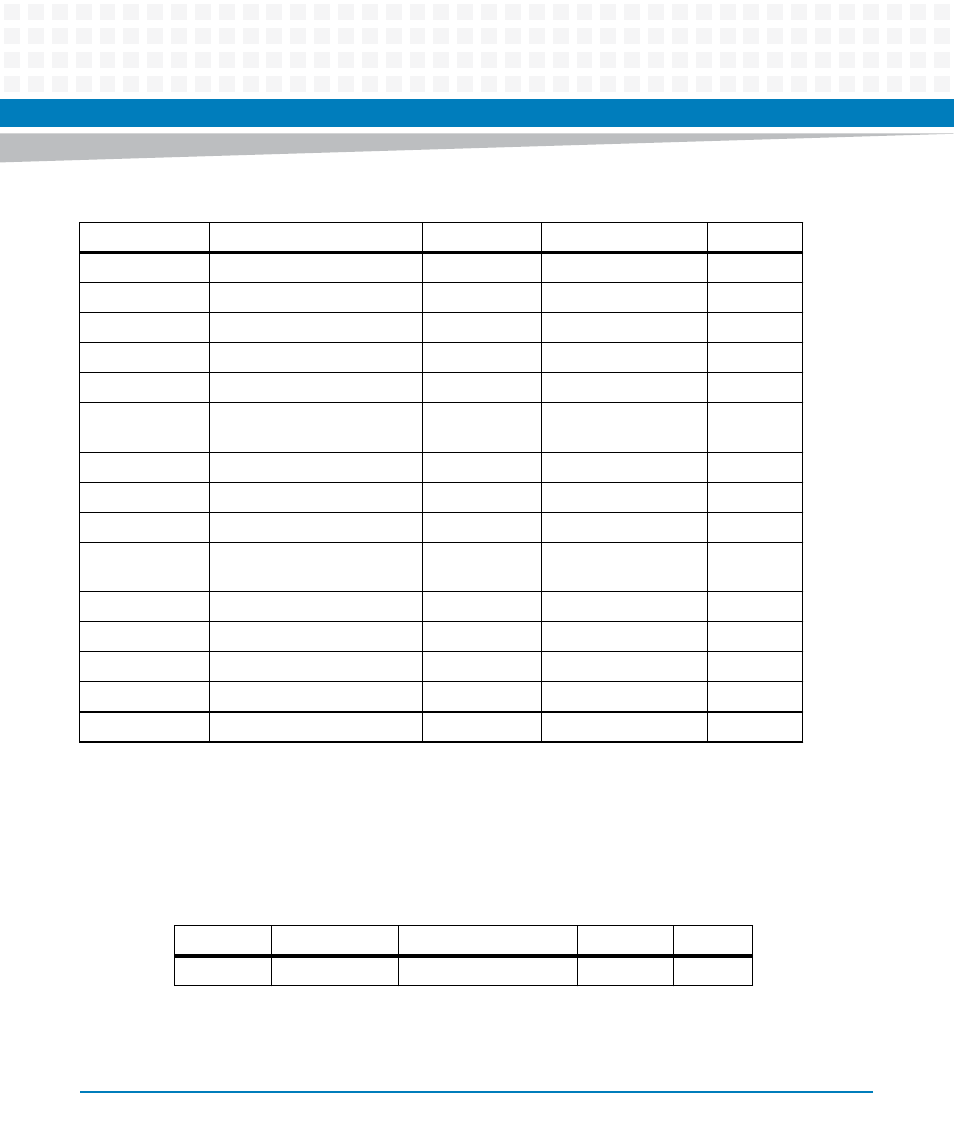

The system and DDR clock is driven by ICS840S07I device. The following table defines the clock

frequency.

BCM54616S

SW_25MHZ_CLK

25Mhz

ICS83905AGILF

+3.3V

XMC

CLK_XMC1

100MHz

ICS9FG108

DIFF

QorIQ P2020

SD_REF_CLK

100MHz

ICS9FG109

DIFF

TSI384

CLK_PCIEC1

100MHz

ICS9FG110

DIFF

TSI384

CLK_PCIEC3

100MHz

ICS9FG111

DIFF

88SE9125

CLK_88SE9125_PCIE_100M

HZ

100MHz

ICS9FG112

DIFF

CPLD

CLK_CPLD

1.8432MHz

Oscillator

+3.3V

USB

CLK_USB_1_24MHZ

24MHz

Oscillator

+3.3V

QorIQ P2020

CPU_RTC

1MHz

CPLD

+3.3V

PMC

CLK_PMC1

33/66/100/13

3Mhz

TSI384

+3.3V

TSI148

CLK_PCI_BR3

133Mhz

ICS840S07I

+3.3V

RTC

CLK_32K

32.768KHz

DS32KHz

+3.3V

CPLD

CPU_LCK0

25MHz

QorIQ P2020

+3.3V

QUART

CLK_QUART

1.8432MHz

CPLD

+3.3V

ICS83905

CLK_25MHZ_ICS9FG108

25Mhz

ICS83905AGILF

+3.3V

Table 7-6 Clock Distribution (continued)

Device

Clock Signal

Frequency

Clock Tree Source

VIO

Table 7-7 System Clock

SYSCLK

CORE

CCB Clock (Platform)

DDR3

LBC

100MHz

800/1200 MHz

400 MHz

400MHz

25MHz

- MVME2502 Installation and Use (August 2014) MVME2500 Installation and Use Manual (February 2014) MVME2500 ECC Installation and Use (August 2014) MVME2500 Installation and Use (April 2015) MVME2500 Installation and Use Manual (March 2015) MVME2502 Installation and Use (April 2014) MVME2502 Installation and Use (December 2014)